# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# MITSUBISHI 8-BIT SINGLE-CHIP MICROCOMPUTER 740 FAMILY / 7600 SERIES

# 7630 Group

User's Manual

• Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

| Notes regarding these | materials | 5 |

|-----------------------|-----------|---|

|-----------------------|-----------|---|

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams and charts, represent information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of JAPAN and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

# **REVISION DESCRIPTION LIST**

# 7630 GROUP USER'S MANUAL

| REVISION         DATE         PAGE NEW         OLD           SEP-98         09-98         First Edition           JAN-99         01-99         "CAN controller" is replaced by "CAN Schematics (1) is modified. |                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| JAN-99 01-99 "CAN controller" is replaced by "CAN                                                                                                                                                               |                                |

|                                                                                                                                                                                                                 |                                |

| 1-13 1-13 Schematics (1) is modified                                                                                                                                                                            | I module" in whole documents.  |

|                                                                                                                                                                                                                 |                                |

| 1-14 1-14 Schematics (8) and (11) are corrected                                                                                                                                                                 | ed.                            |

| 1-21 1-21 Replaced:"PUPDJ" with "PUP4J".                                                                                                                                                                        |                                |

| 1-28 1-28 Replaced:"URxD" with "SOUT" .                                                                                                                                                                         |                                |

| Replaced:"URxD" with "SIN".                                                                                                                                                                                     |                                |

| 1-38 1-38 Fig.41 is modified.                                                                                                                                                                                   |                                |

| 1-41 1-41 Replaced:"FFFBH" with "FFFB16".                                                                                                                                                                       |                                |

| Replaced:"FFFAH" with "FFFA16".                                                                                                                                                                                 | (00)         ( 400 - 70)     - |

| 3-4 Values changed:lih (35,113) to (20,2                                                                                                                                                                        |                                |

| (-200,-20);typical values are remove                                                                                                                                                                            | ed.                            |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

|                                                                                                                                                                                                                 |                                |

# **Preface**

This user's manual describes Mitsubishi's CMOS 8-bit microcomputers 7630 Group.

After reading this manual, the user should have a through knowledge of the functions and features of the 7630 Group, and should be able to fully utilize the product. The manual starts with specifications and ends with application examples.

For details of software, refer to the "SERIES MELPS 7600 <SOFTWARE> USER'S MANUAL."

For details of development support tools, refer to the "DEVELOPMENT SUPPORT TOOLS FOR MICROCOMPUTERS" data book.

# **BEFORE USING THIS USER'S MANUAL**

This user's manual consists of the following three chapters. Refer to the chapter appropriate to your conditions, such as hardware design or software development. Chapter 3 also includes necessary information for systems denelopment. Be sure to refer to this chapter.

## 1. Organization

#### CHAPTER 1 HARDWARE

This chapter describes features of the microcomputer and operation of each peripheral function.

#### CHAPTER 2 APPLICATION

This chapter describes usage and application examples of peripheral functions, based mainly on setting examples of related registers.

#### CHAPTER 3 APPENDIX

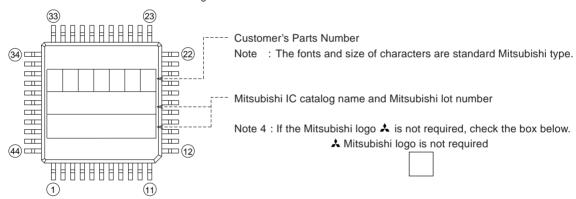

This chapter includes necessary information for systems development using the microcomputer, electric characteristics, a list of registers, the masking confirmation (mask ROM version), and mark specifications which are to be submitted when ordering.

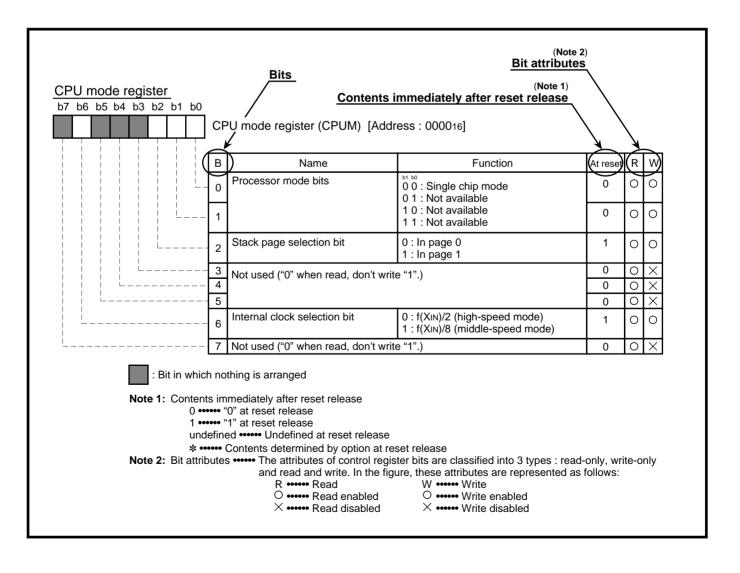

# 2. Structure of register

The figure of each register structure describes its functions, contents at reset, and attributes as follows :

# **Table of contents**

| CHAPIER I. HARDWARE                                 |      |

|-----------------------------------------------------|------|

| DESCRIPTION                                         | 1-2  |

| FEATURES                                            | 1-2  |

| APPLICATION                                         |      |

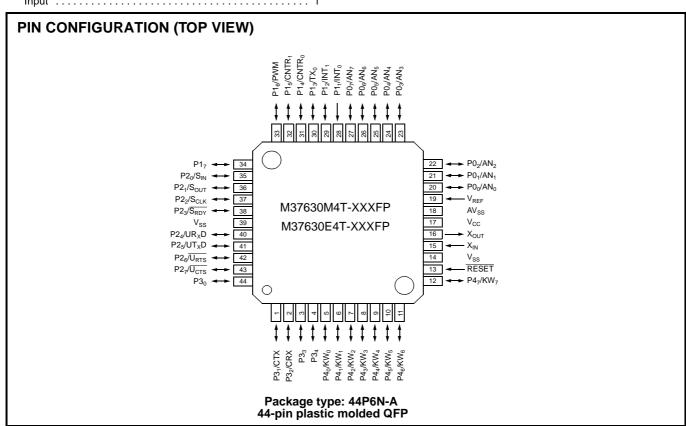

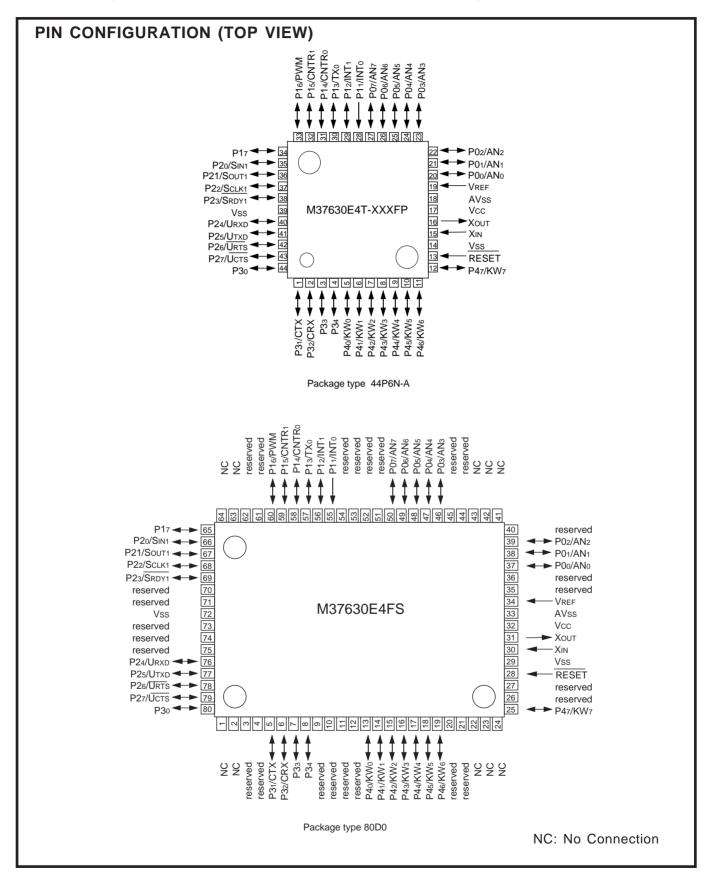

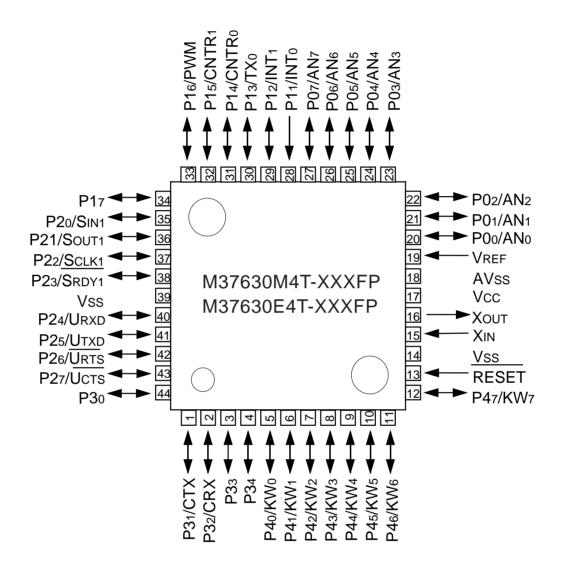

| PIN CONFIGURATION                                   |      |

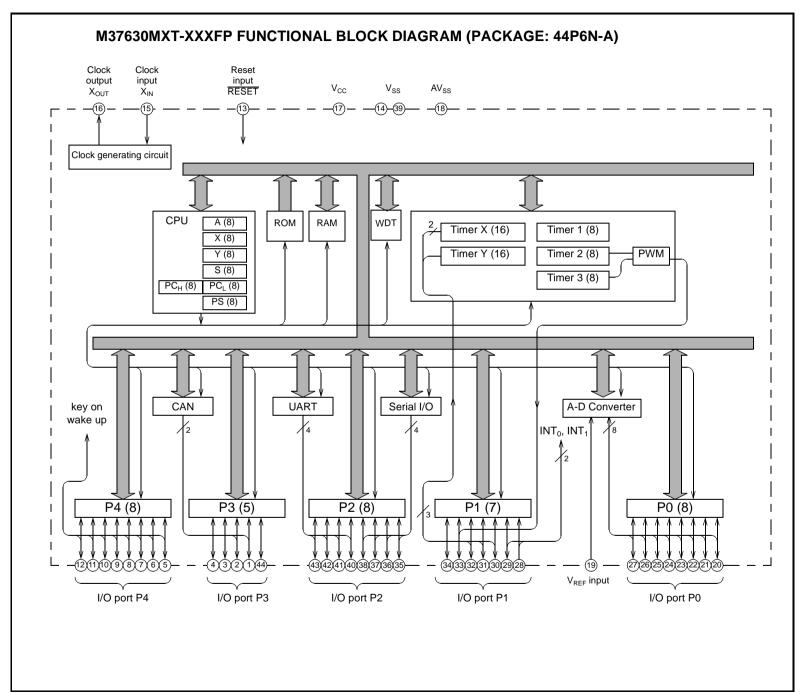

| FUNCTIONAL BLOCK DIAGRAM                            | 1-3  |

| PIN DESCRIPTION                                     | 1-4  |

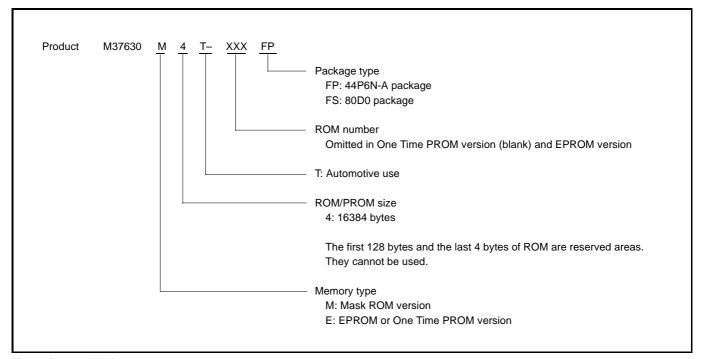

| PART NUMBERING                                      | 1-5  |

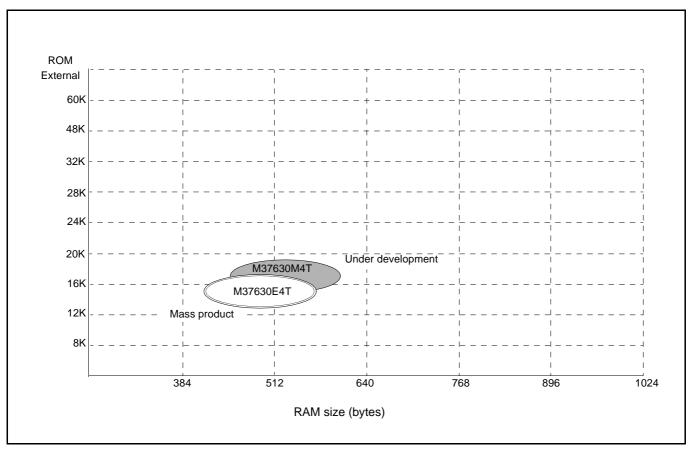

| GROUP EXPANSION                                     |      |

| Memory Type                                         |      |

| Memory Size                                         |      |

| Package                                             |      |

| FUNCTIONAL DESCRIPTION                              | 1-7  |

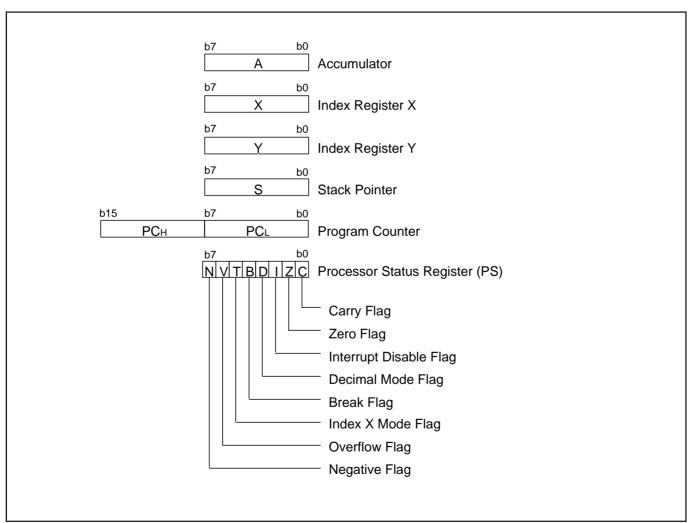

| Central Processing Unit (CPU)                       |      |

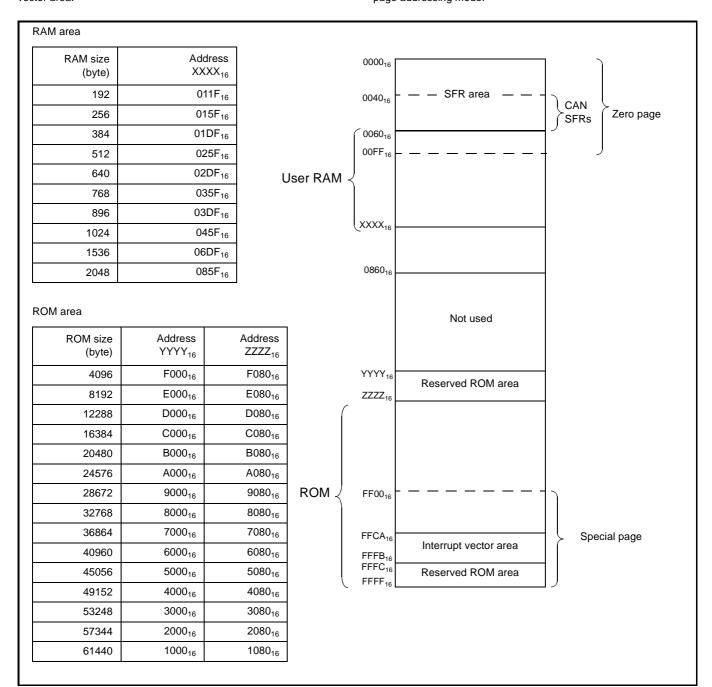

| Memory                                              | 1-11 |

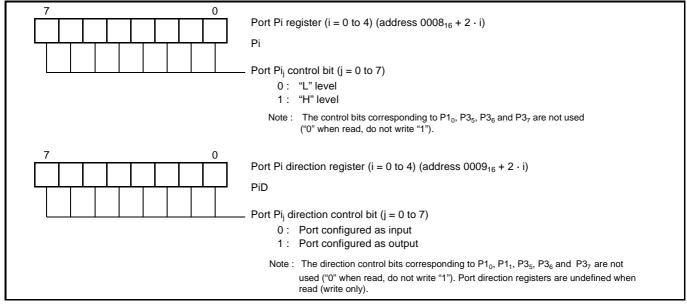

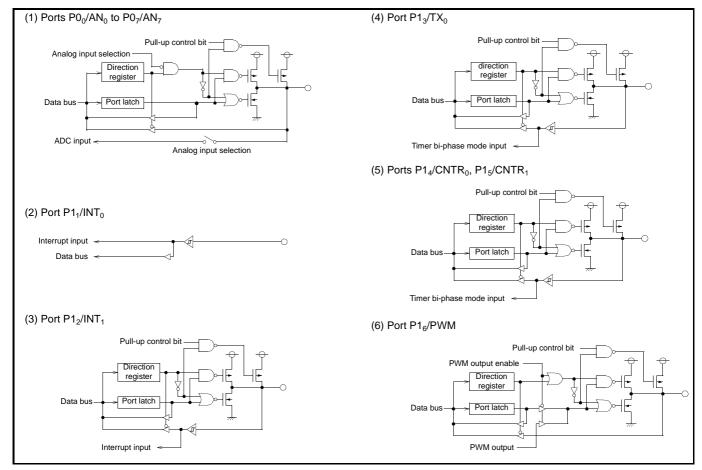

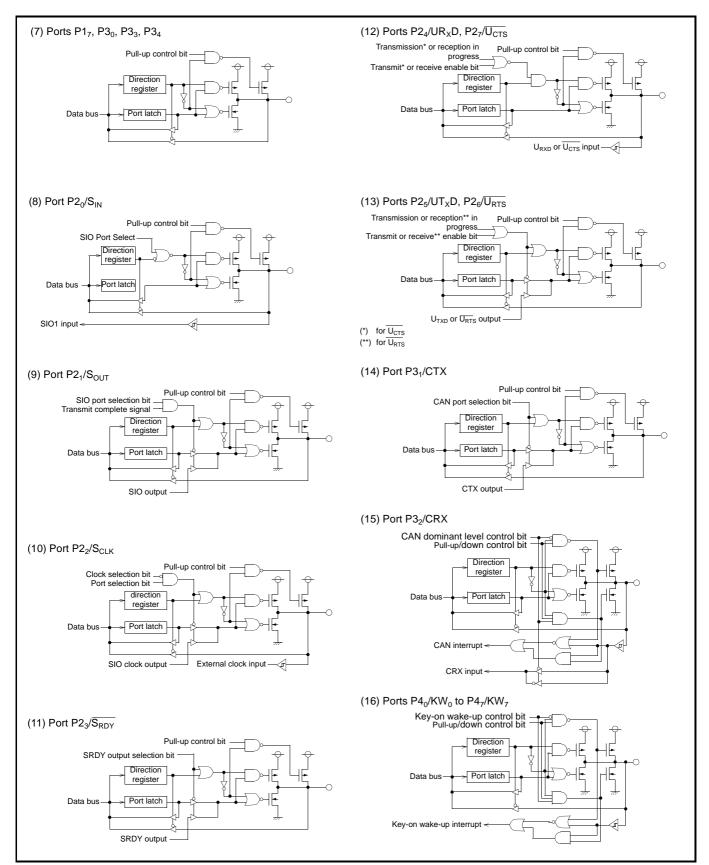

| I/O Ports                                           | 1-13 |

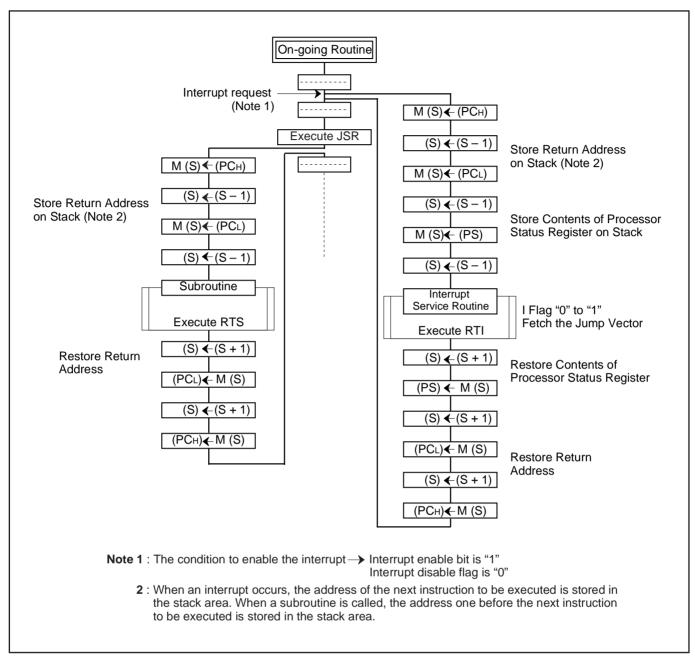

| Interrupts                                          |      |

| Key-on Wake-up                                      |      |

| Timers                                              |      |

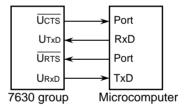

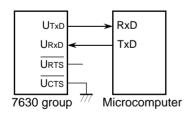

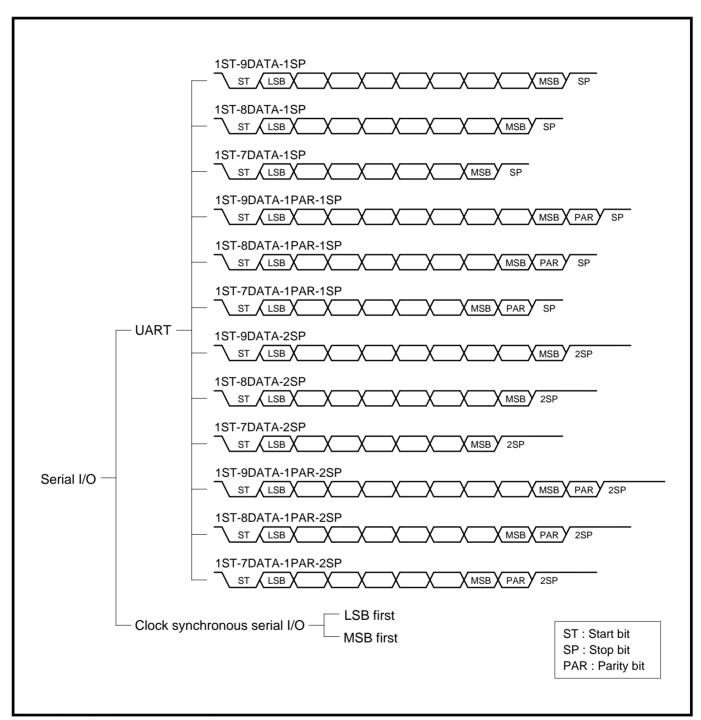

| Serial I/Os                                         |      |

| CAN Module                                          |      |

| A-D Converter                                       |      |

| Watchdog Timer                                      |      |

| Reset Circuit                                       |      |

| Clock Generating Circuit                            |      |

| Data Required for Mask Orders                       |      |

| Absolute Maximum Rating                             |      |

| Electrical Characteristics                          |      |

| A-D Converter Characteristics                       |      |

| Timing Requirements                                 |      |

| Switching Characteristics                           |      |

| Timing Diagram                                      | 1-50 |

| CHAPTER 2. APPLICATION                              |      |

| 2.1 I/O ports                                       | 2-2  |

| 2.1.1 Memory map of I/O ports                       |      |

| 2.1.2 Related registers                             |      |

| 2.1.3 Overvoltage conditions at digital input ports |      |

| 2.1.4 Handling examples of unused pins              |      |

| 2.2 Interrupts                                      |      |

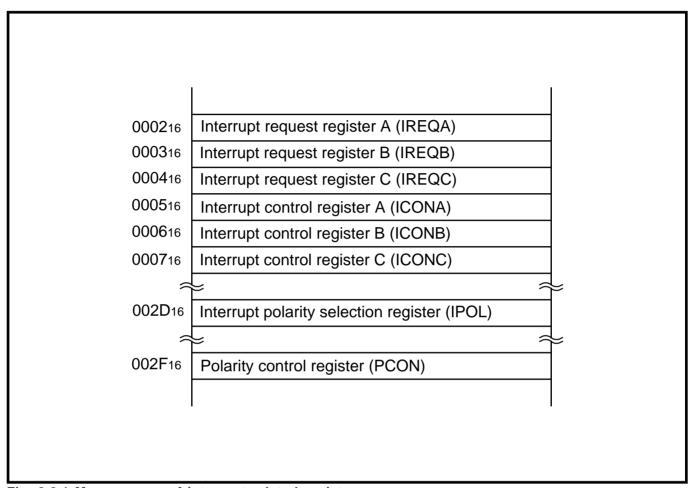

| 2.2.1 Memory map of interrupt related registers     |      |

| 2.2.2 Related registers                             |      |

| 2.2.3 Interrupt setting method                      |      |

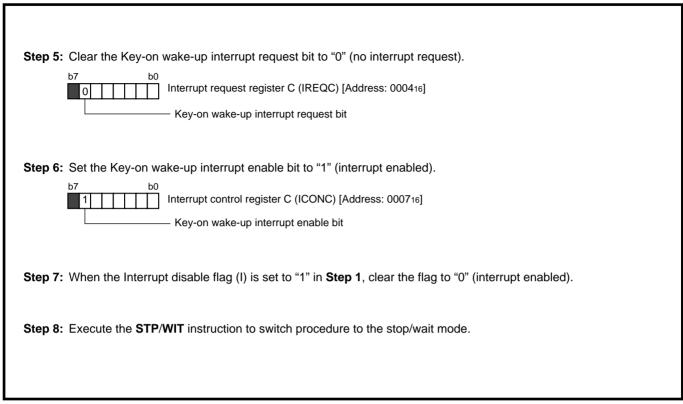

| 2.2.4 Key-on wake-up interrupt                      |      |

| 2.3 Timers                                          |      |

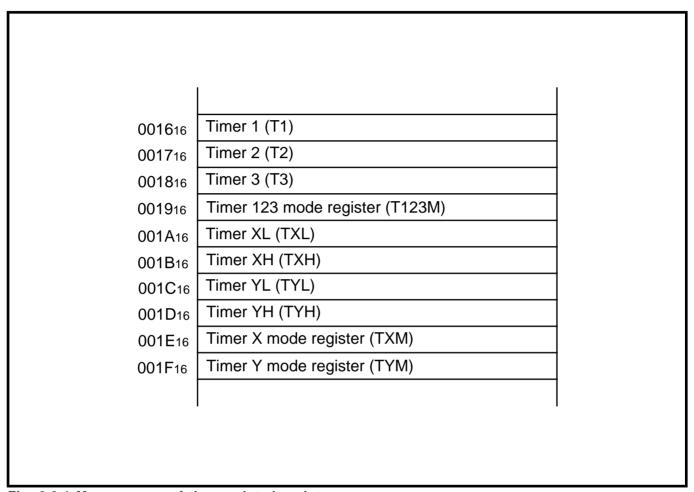

| 2.3.1 Memory map of timer                           |      |

| 2.3.2 Related registers                             |      |

| 2.3.3 Timer application examples                    |      |

|                                                     |      |

| 2-34       |

|------------|

| 2-34       |

| 2-35       |

| 2-37       |

| 2-48       |

| 2-50       |

| 2-53       |

| 2-54       |

| 2-55       |

| 2-60       |

| 2-62       |

| 2-65       |

| 2-65       |

| 2-66       |

| 2-67       |

| 2-67       |

| 2-68       |

| 2-72       |

| 2-74       |

| 2-75       |

| 2-90       |

| 2-90       |

| 2-91       |

| 2-92       |

| 2-93       |

| 2-93       |

| 2-94       |

| 2-94       |

| 2-95       |

| 2-95       |

| 2-96       |

| 2-97       |

| 2-97       |

| 2-98       |

| 2-99       |

| . 2-100    |

| . 2-101    |

| .2-101     |

| .2-102     |

| .2-103     |

| .2-104     |

|            |

| 3-2        |

| 3-2        |

| 3-3        |

| 3-3<br>3-4 |

| 3-4<br>3-5 |

| 3-5<br>3-5 |

| 3-3<br>3-6 |

| 3-8        |

| 3-8        |

|            |

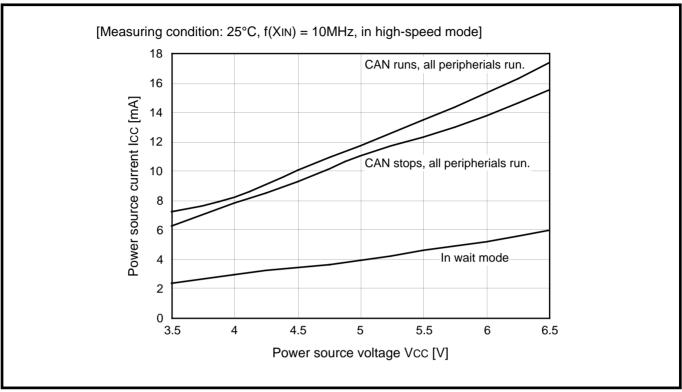

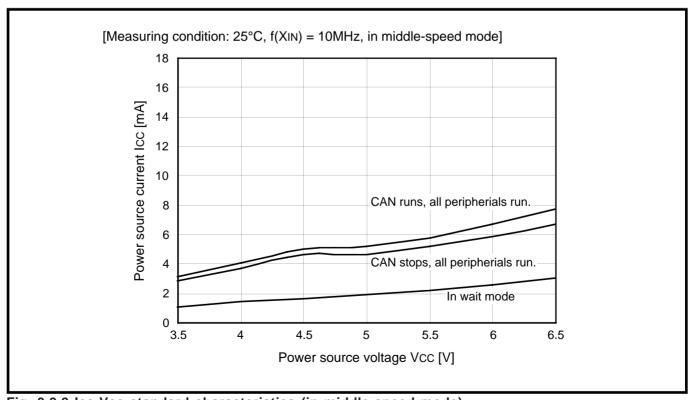

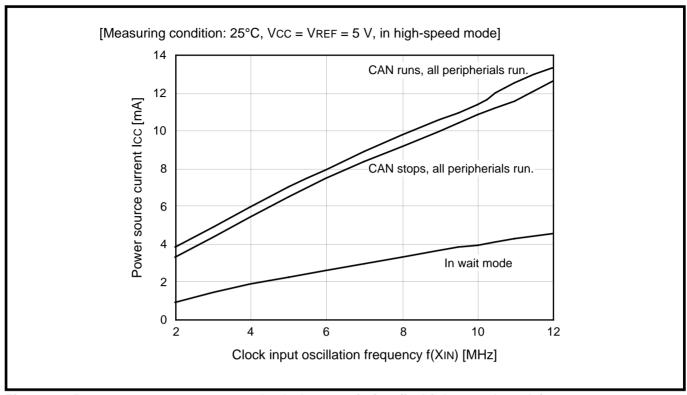

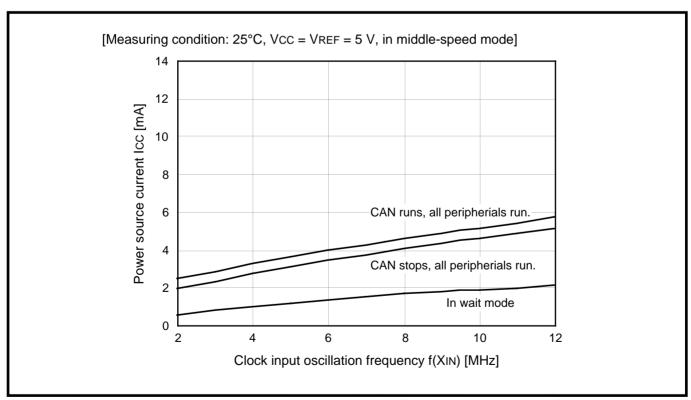

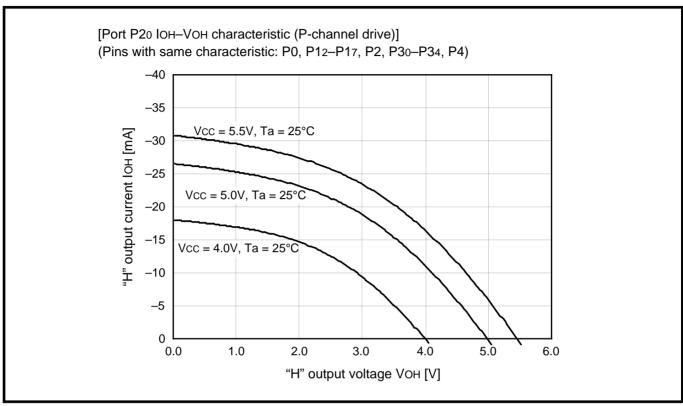

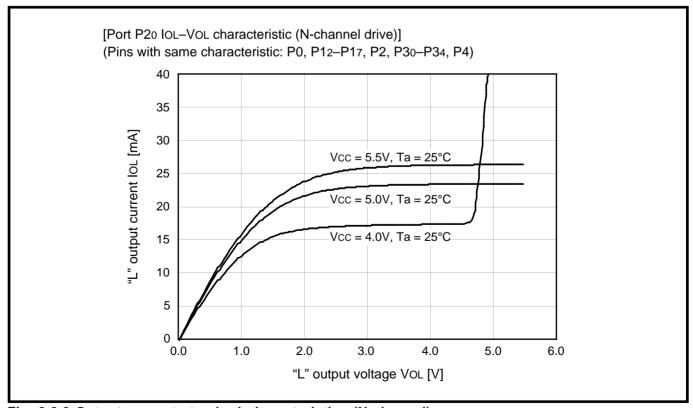

| 3.2.2 Output current standard characteristics                               | 3-10 |

|-----------------------------------------------------------------------------|------|

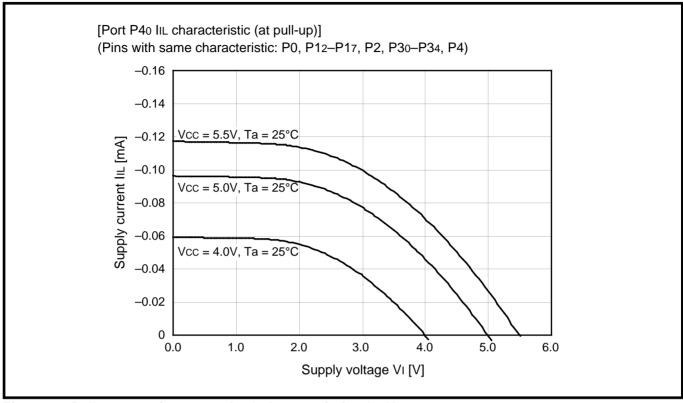

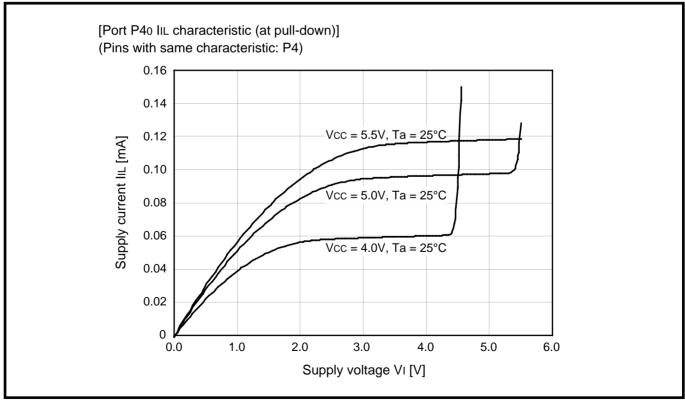

| 3.2.3 Input current standard characteristics                                | 3-11 |

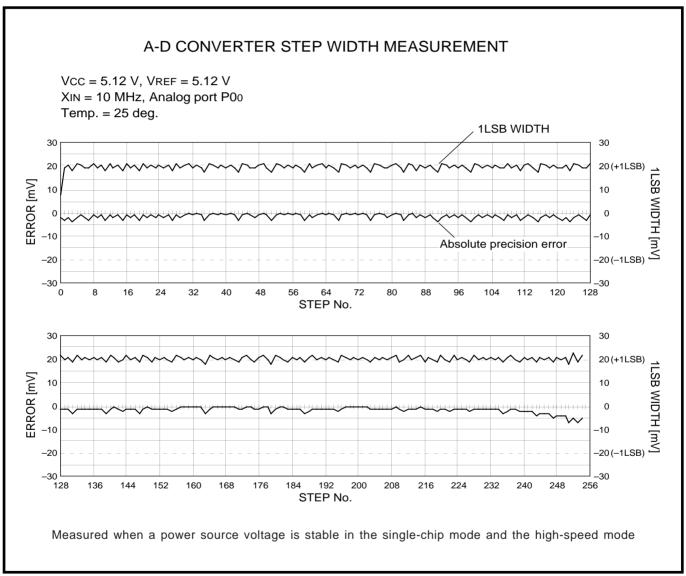

| 3.2.4 A-D conversion standard characteristics                               |      |

| 3.3 Notes on use                                                            |      |

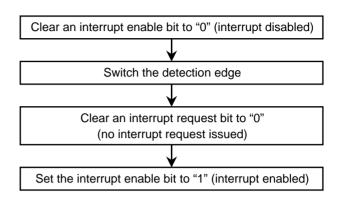

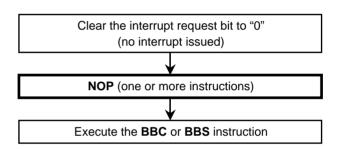

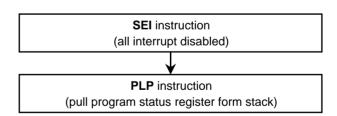

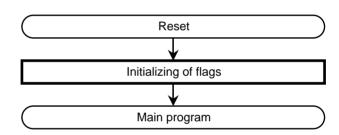

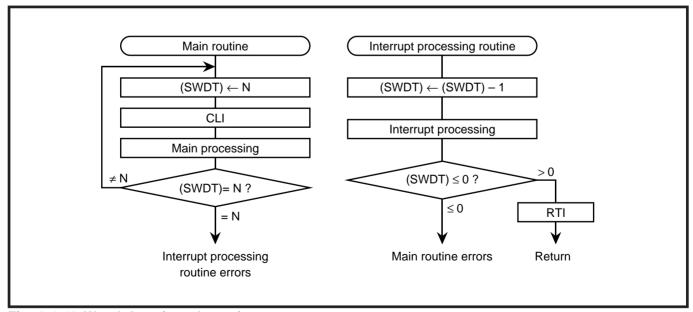

| 3.3.1 Notes on interrupts                                                   | 3-13 |

| 3.3.2 Notes on A-D converter                                                |      |

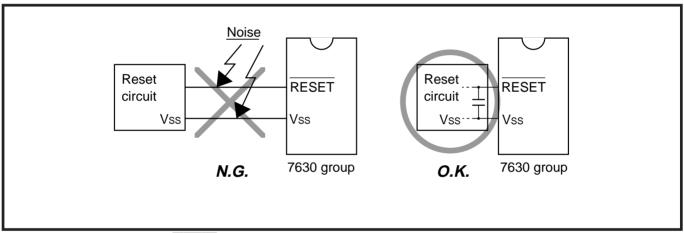

| 3.3.3 Notes on RESET pin                                                    | 3-14 |

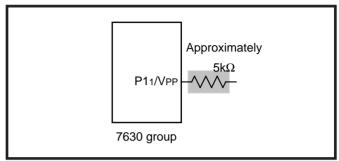

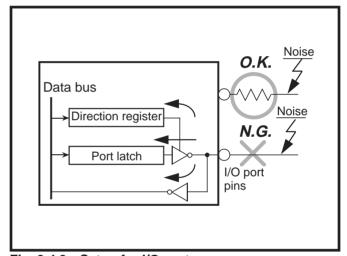

| 3.3.4 Notes on input and output pins                                        | 3-14 |

| 3.3.5 Notes on programming                                                  |      |

| 3.4 Countermeasures against noise                                           |      |

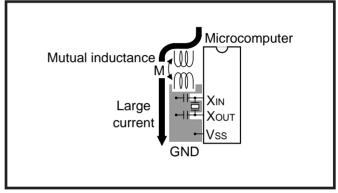

| 3.4.1 Shortest wiring length                                                | 3-17 |

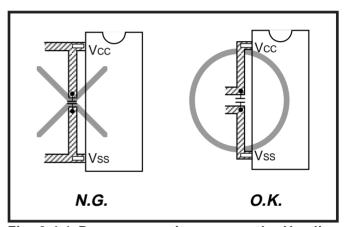

| 3.4.2 Connection of a bypass capacitor across the Vss line and the Vcc line | 3-18 |

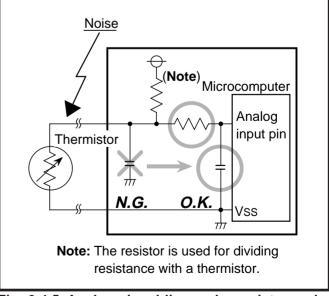

| 3.4.3 Wiring to analog input pins                                           | 3-18 |

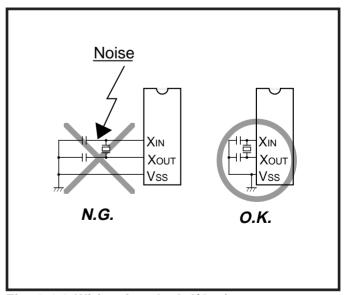

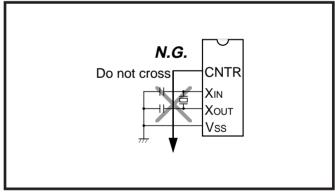

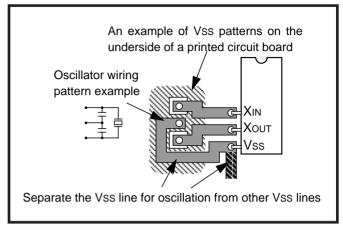

| 3.4.4 Consideration for oscillator                                          | 3-19 |

| 3.4.5 Setup for I/O ports                                                   | 3-20 |

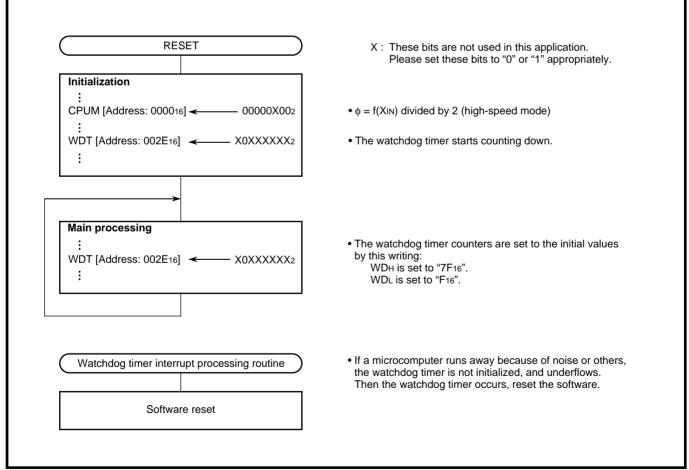

| 3.4.6 Providing of watchdog timer function by software                      | 3-21 |

| 3.5 List of registers                                                       | 3-22 |

| 3.6 Mask ROM ordering method                                                | 3-49 |

| 3.7 Mark specification form                                                 | 3-51 |

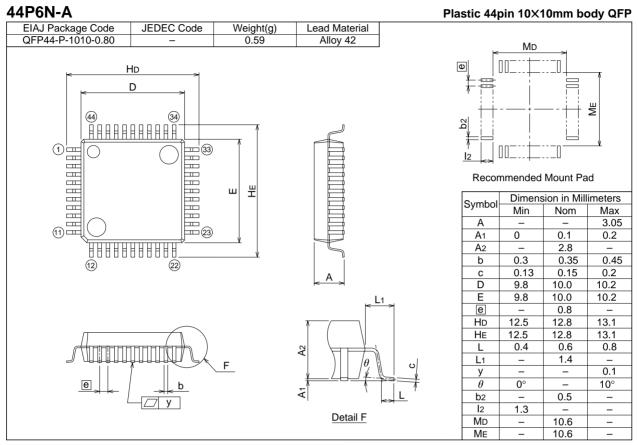

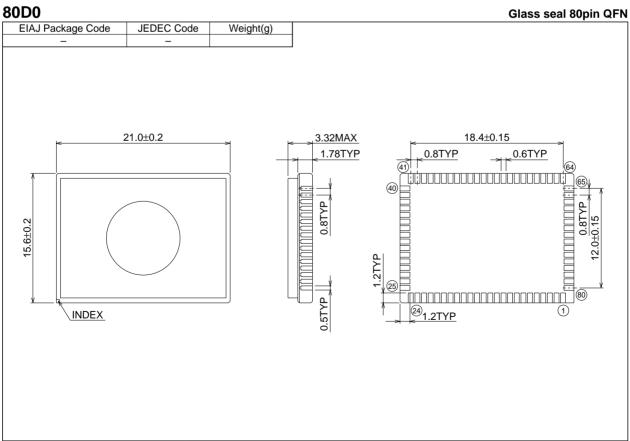

| 3.8 Package outline                                                         | 3-52 |

| 3.9 List of instruction codes                                               | 3-53 |

| 3.10 Machine instructions                                                   | 3-54 |

| 3.11 SFR memory map                                                         | 3-64 |

| 3.12 Pin configuration                                                      | 3-65 |

# List of figures

| _          |            |

|------------|------------|

| ALLABTED 4 | . HARDWARF |

| <i>'</i> ' |            |

|            |            |

| Fig. 1 | Pin configuration of M37630M4T-XXXFP                              | . 1-2 |

|--------|-------------------------------------------------------------------|-------|

| Fig. 2 | Prunctional block diagram                                         | . 1-3 |

| Fig. 3 | Part numbering                                                    | . 1-5 |

| Fig. 4 | Memory expansion plan                                             | . 1-6 |

|        | 5 740 Family CPU register structure                               |       |

| Fig. 6 | Register push and pop at interrupt generation and subroutine call | . 1-8 |

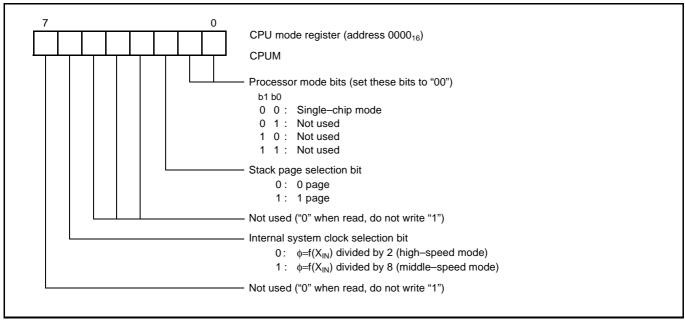

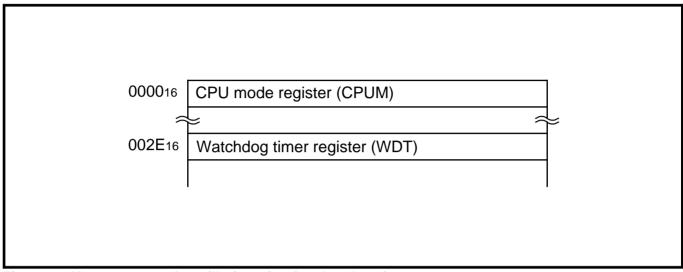

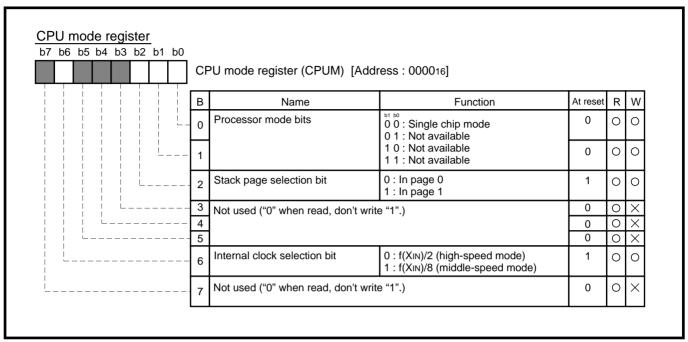

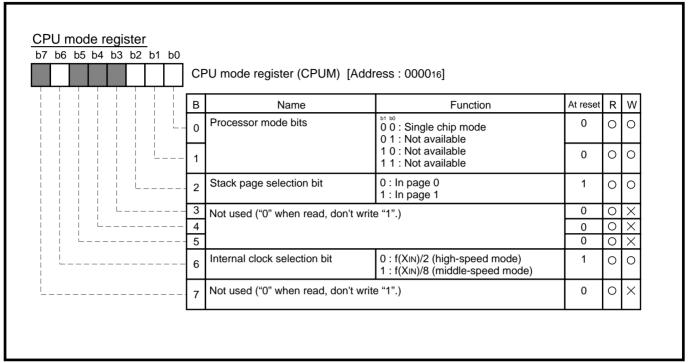

| Fig. 7 | Structure of CPU mode register                                    | 1-10  |

|        | B Memory map diagram                                              |       |

| Fig. 9 | Memory map of special register (SFR)                              | 1-12  |

| Fig. 1 | 0 Structure of Port- and Port direction registers                 | 1-13  |

| Fig. 1 | 1 Structure of Port I/Os (1)                                      | 1-13  |

| Fig. 1 | 2 Structure of Port I/Os (2)                                      | 1-14  |

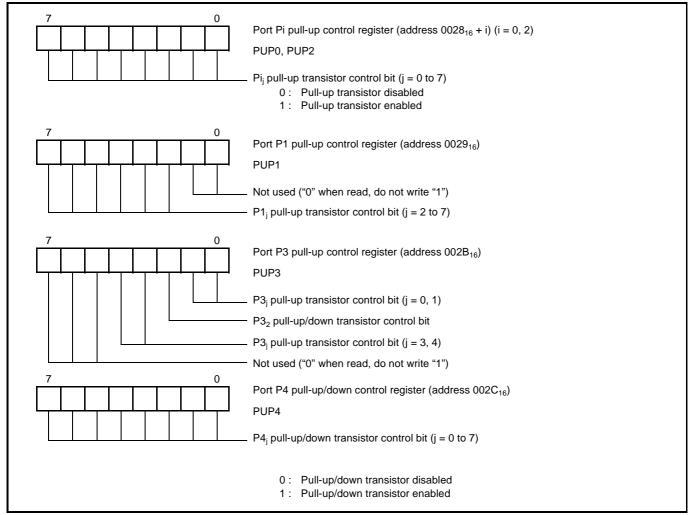

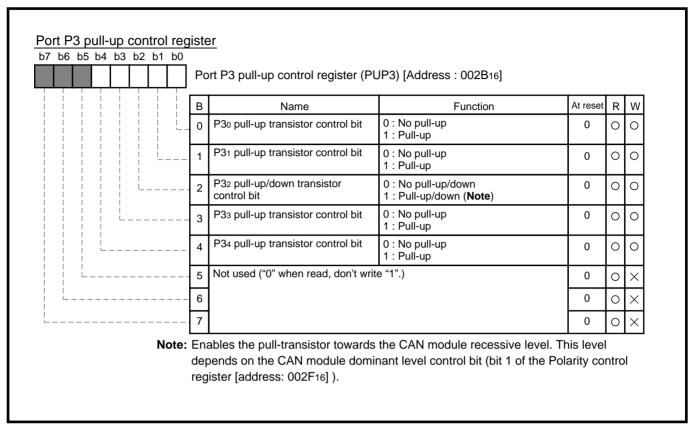

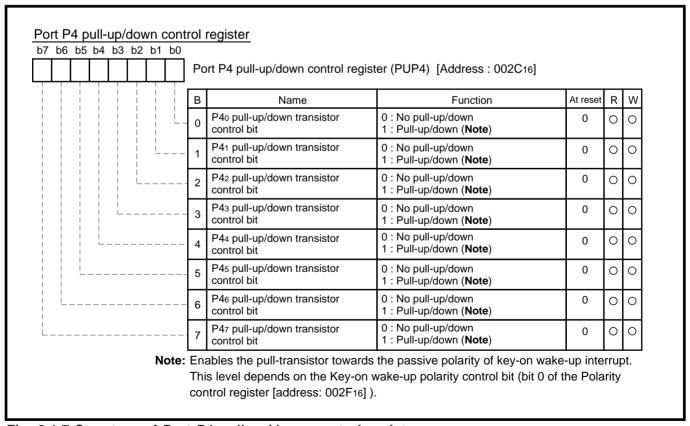

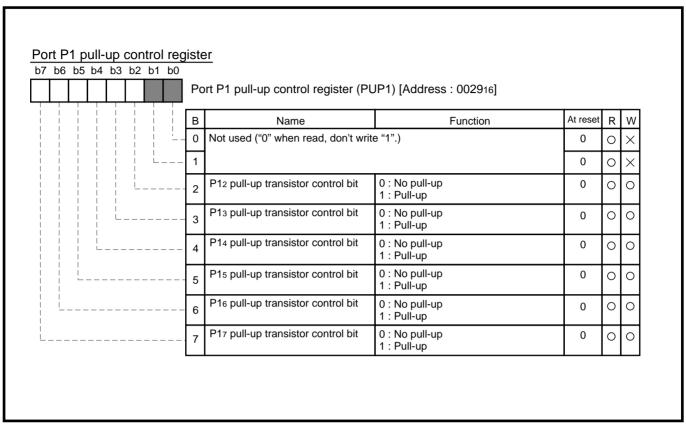

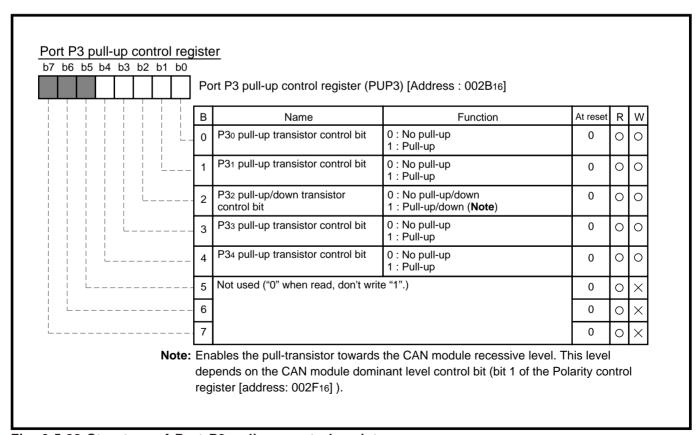

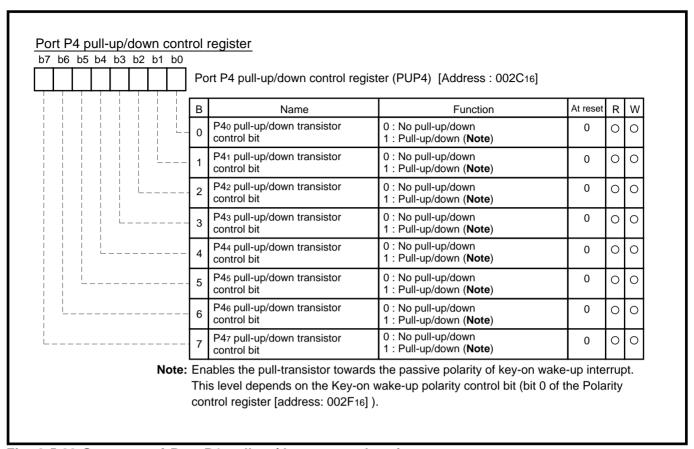

| Fig. 1 | 3 Structure of Port pull-up/down control registers                | 1-15  |

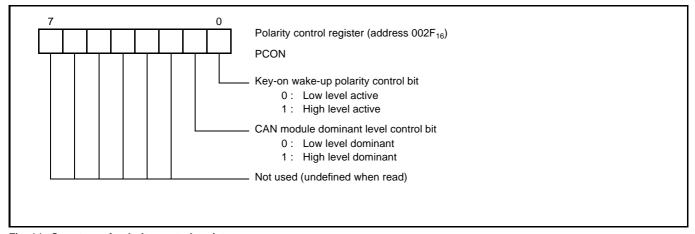

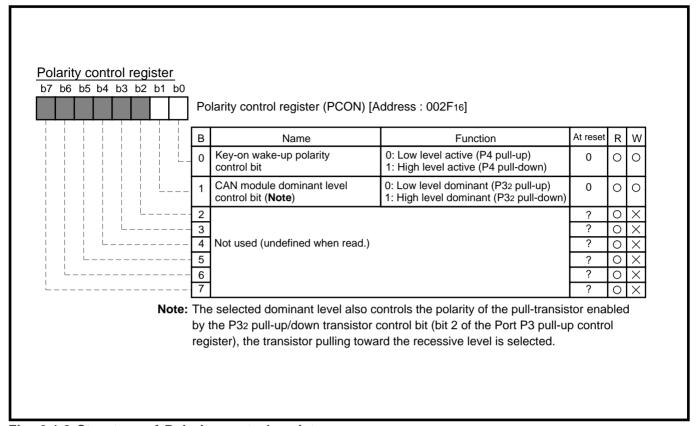

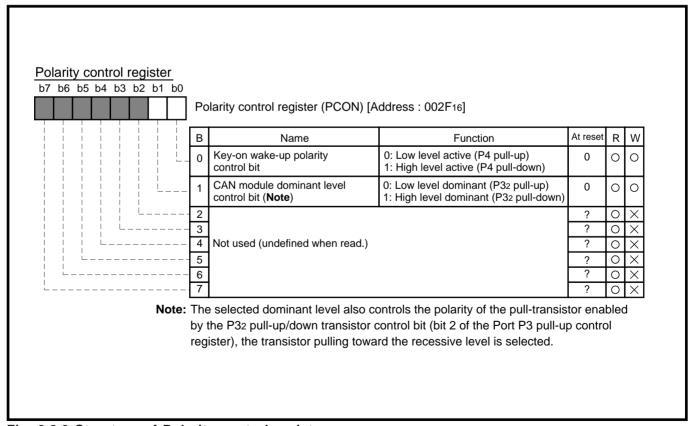

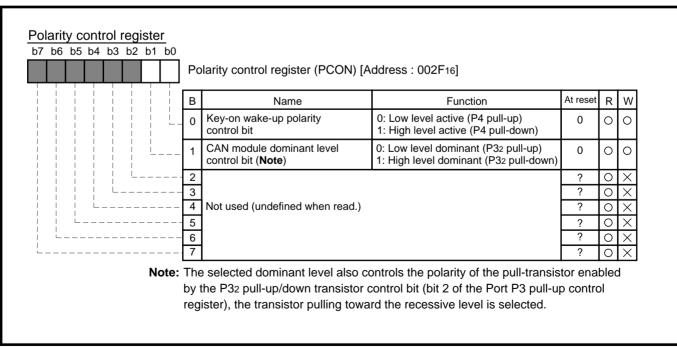

| -      | 4 Structure of Polarity control register                          |       |

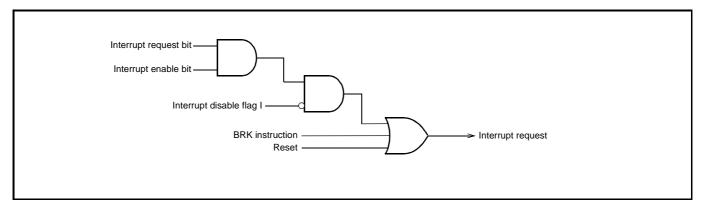

| Fig. 1 | 5 Interrupt control                                               | 1-19  |

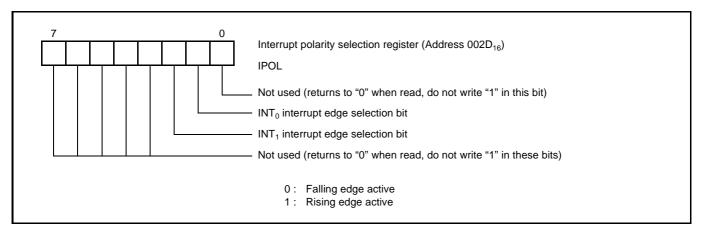

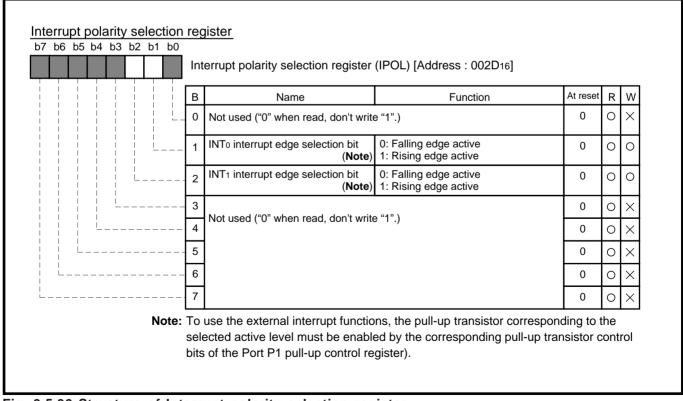

|        | 6 Structure of Interrupt polarity selection register              |       |

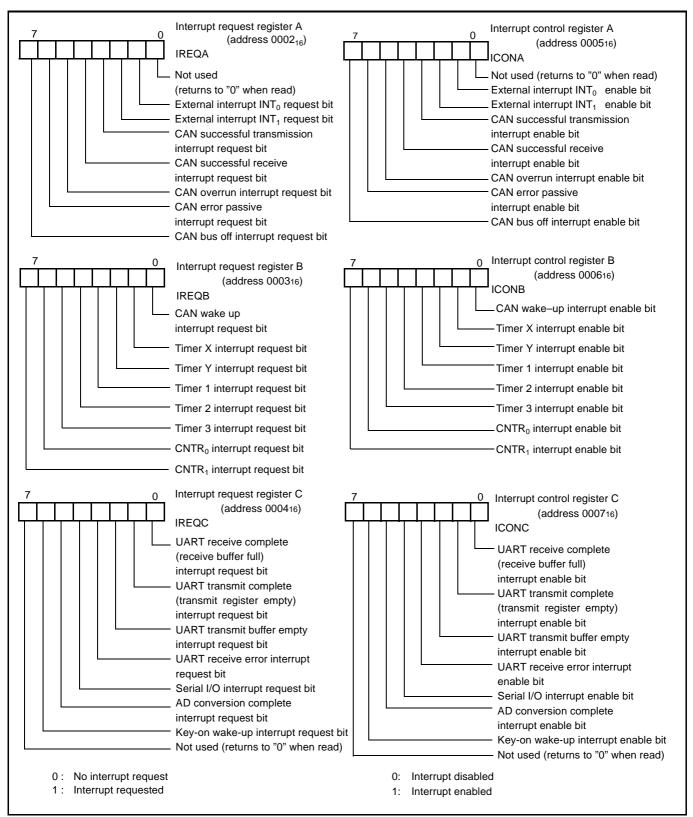

| Fig. 1 | 7 Structure of Interrupt request and control registers A, B and C | 1-20  |

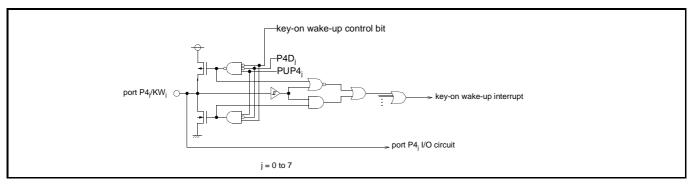

|        | 8 Block diagram of key-on wake-up circuit                         |       |

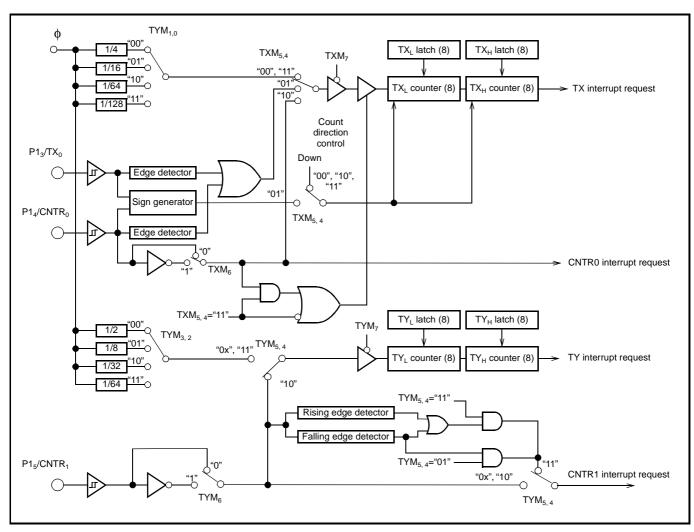

| Fig. 1 | 9 Block diagram of timers X and Y                                 | 1-22  |

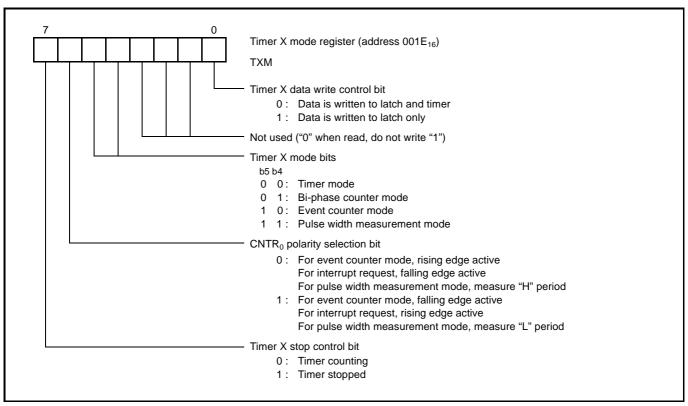

|        | 20 Structure of Timer X mode register                             |       |

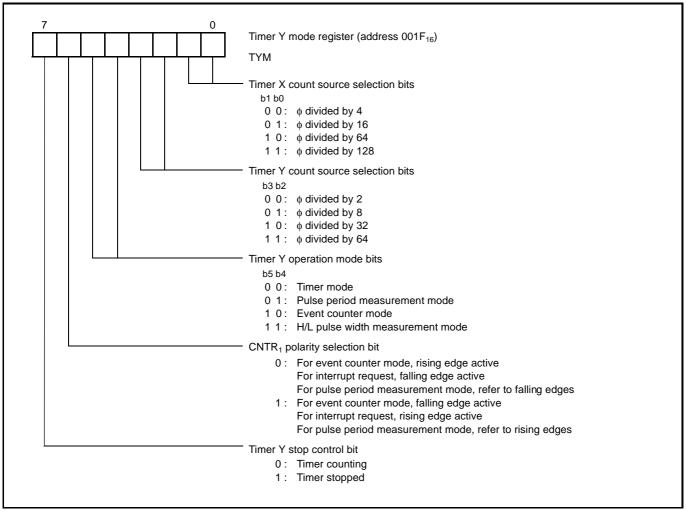

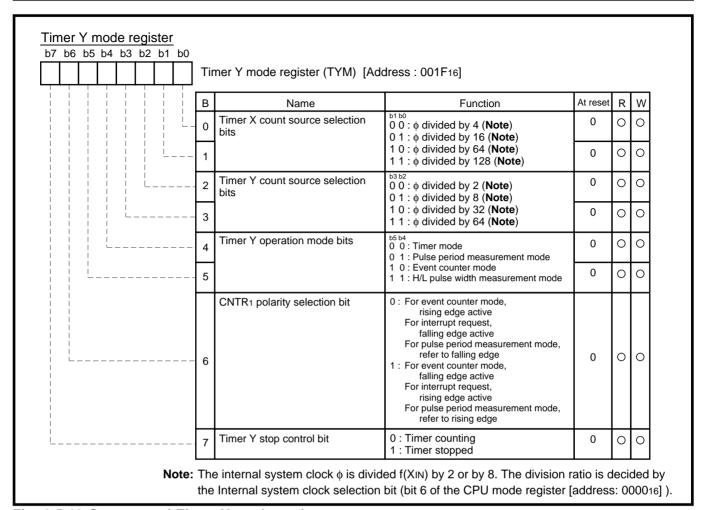

| Fig. 2 | 21 Structure of Timer Y mode register                             | 1-24  |

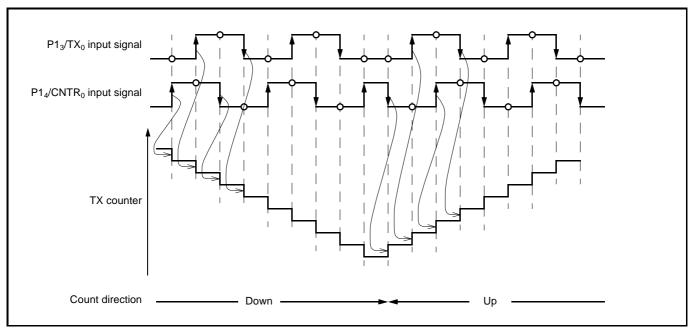

|        | 22 Timer X bi-phase counter mode operation                        |       |

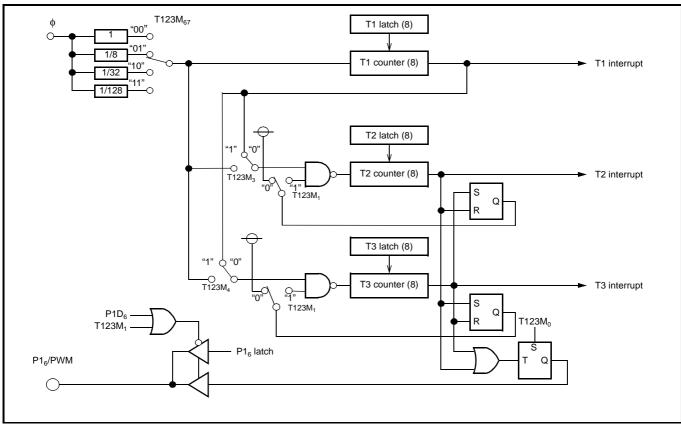

|        | 23 Block diagram of timers 1 to 3                                 |       |

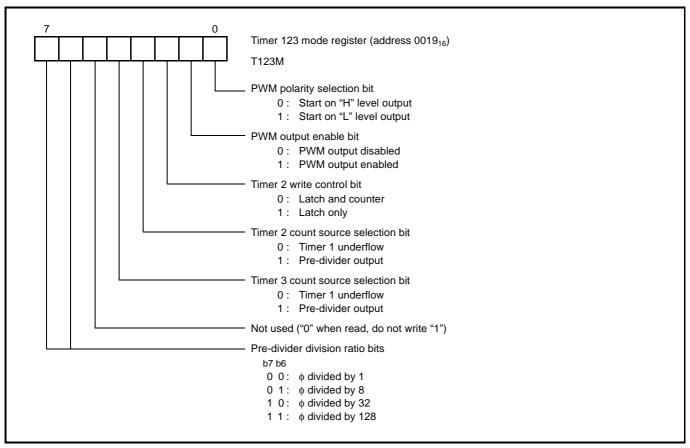

| Fig. 2 | 24 Timer 123 mode register configulation                          | 1-27  |

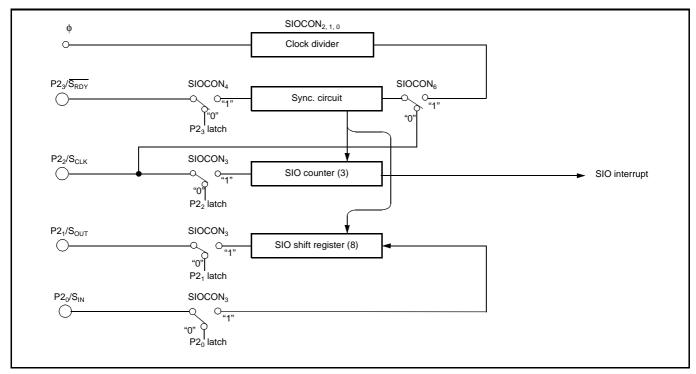

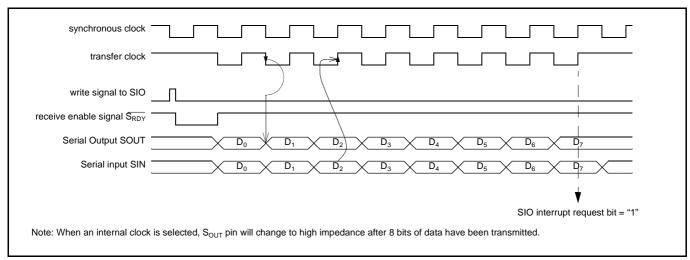

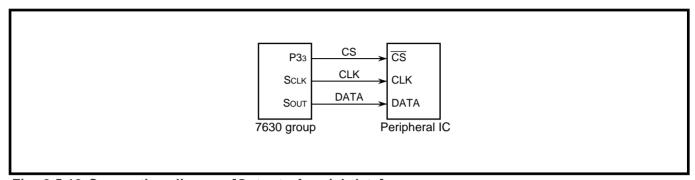

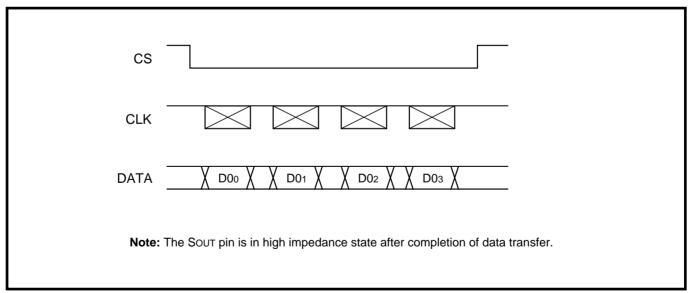

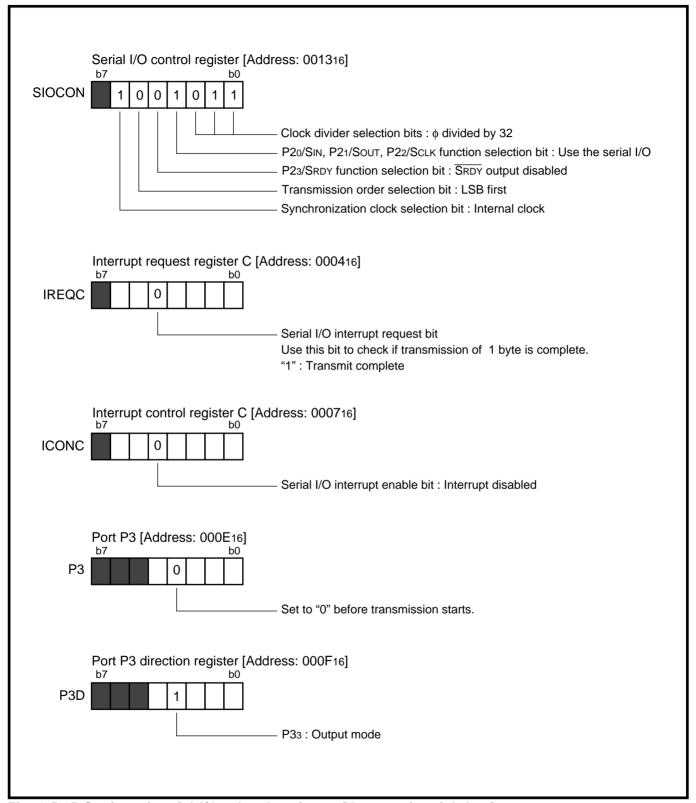

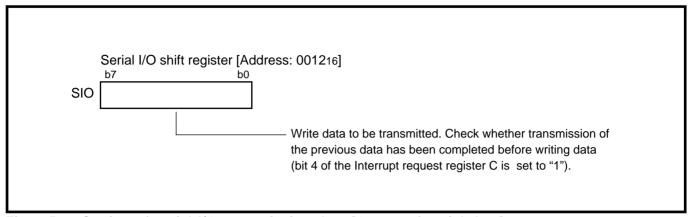

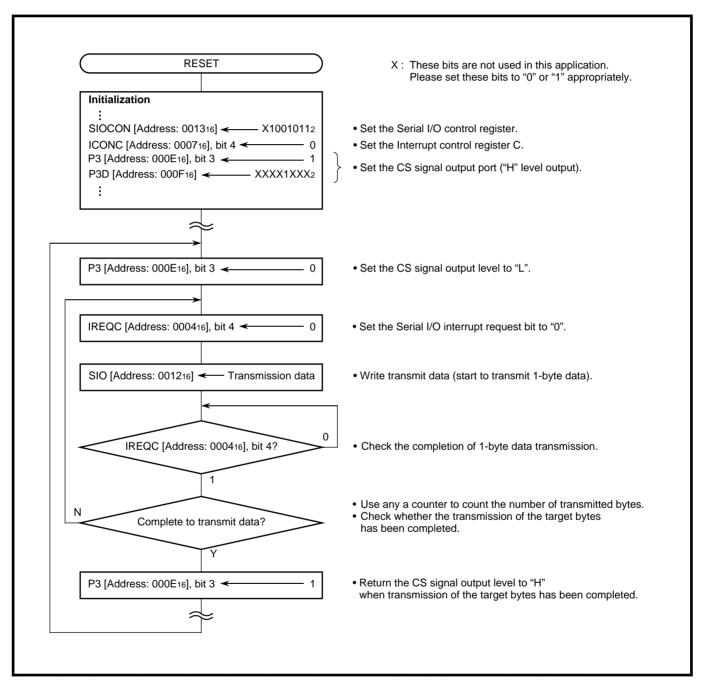

| Fig. 2 | 25 Block diagram of clock syncronous SI/O                         | 1-28  |

| Fig. 2 | 26 Timing of clock syncronous SI/O function                       | 1-28  |

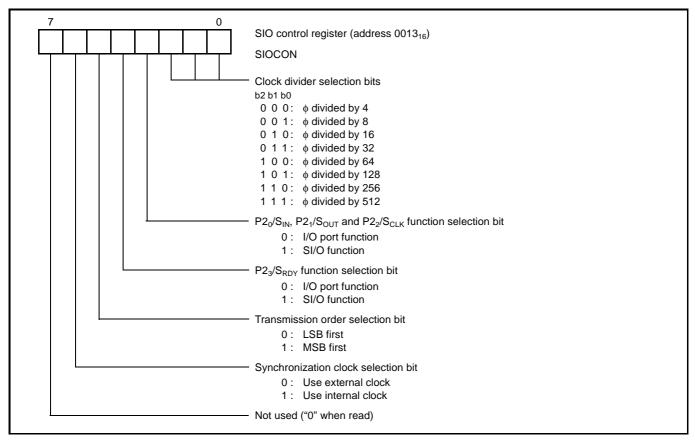

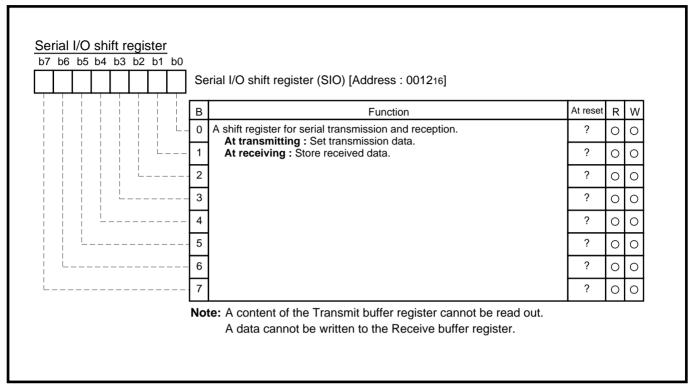

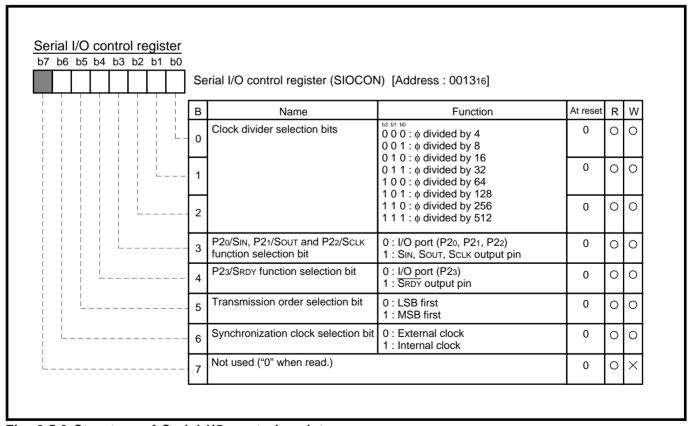

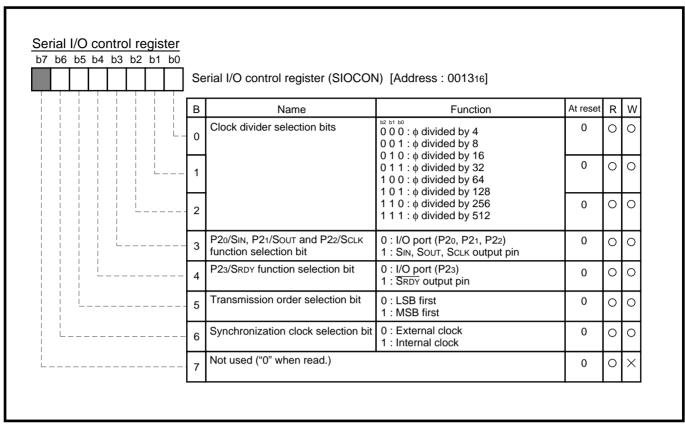

| Fig. 2 | 27 Structure of Serial I/O control register                       | 1-29  |

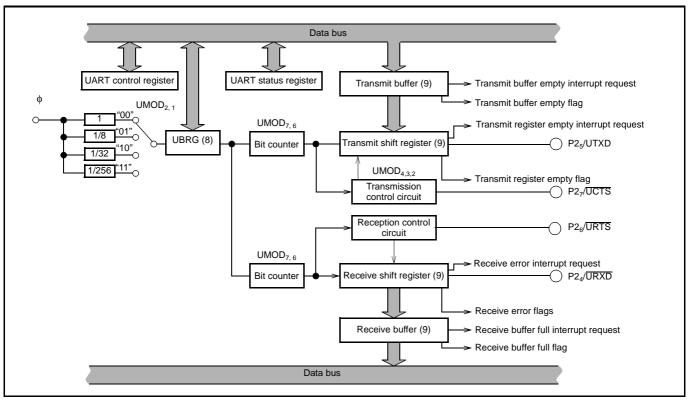

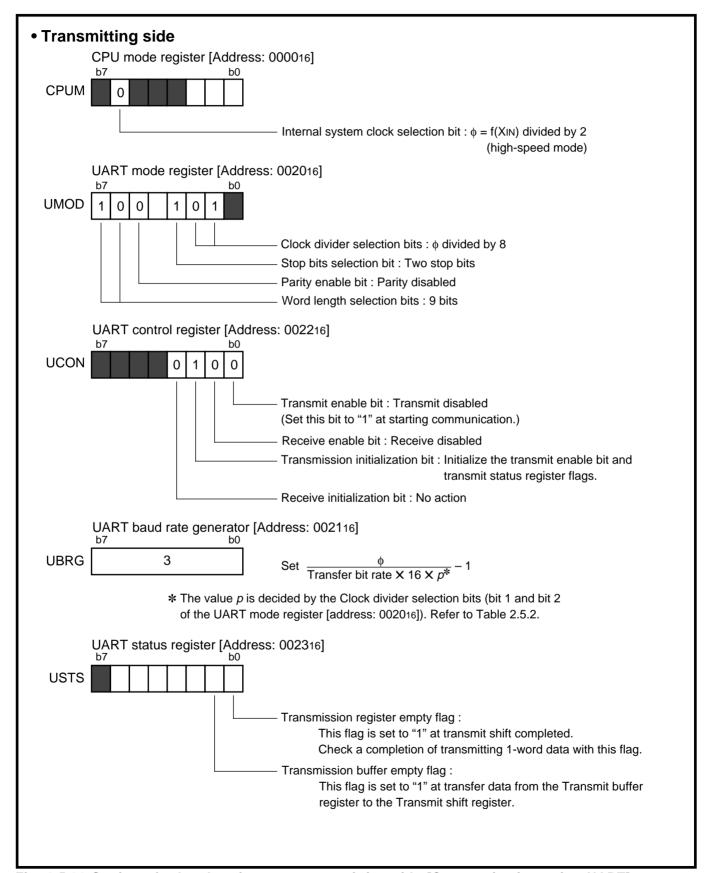

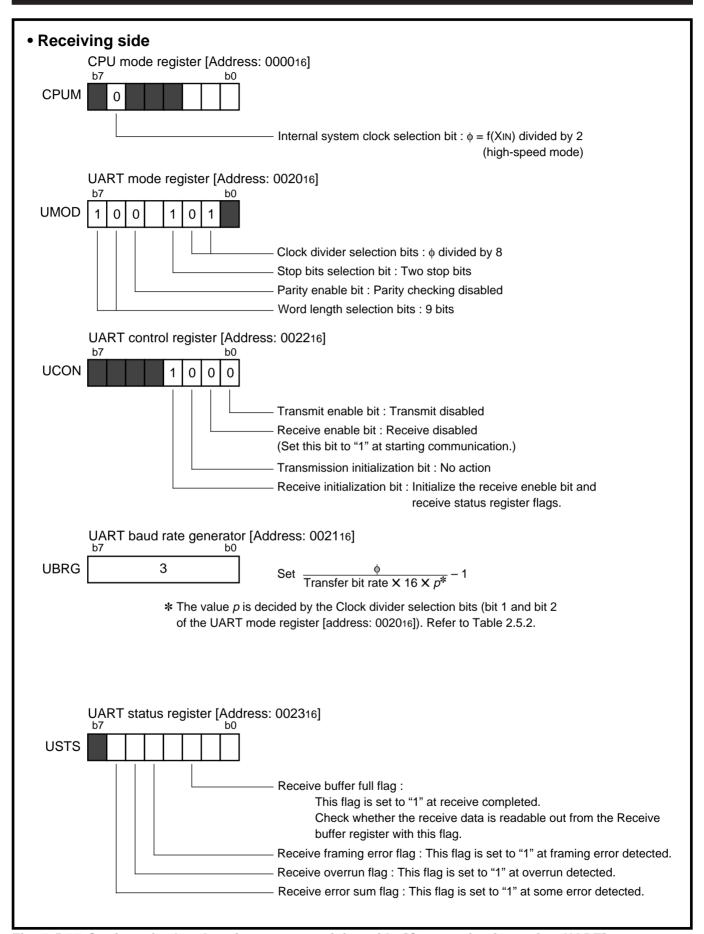

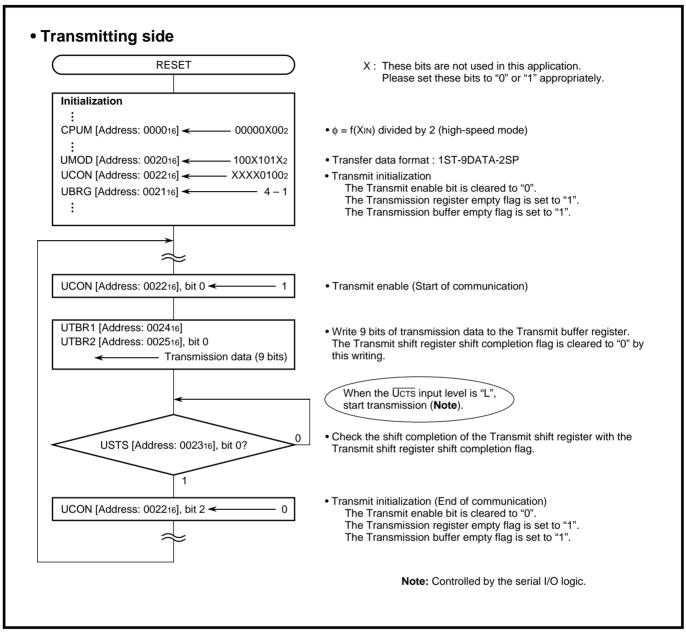

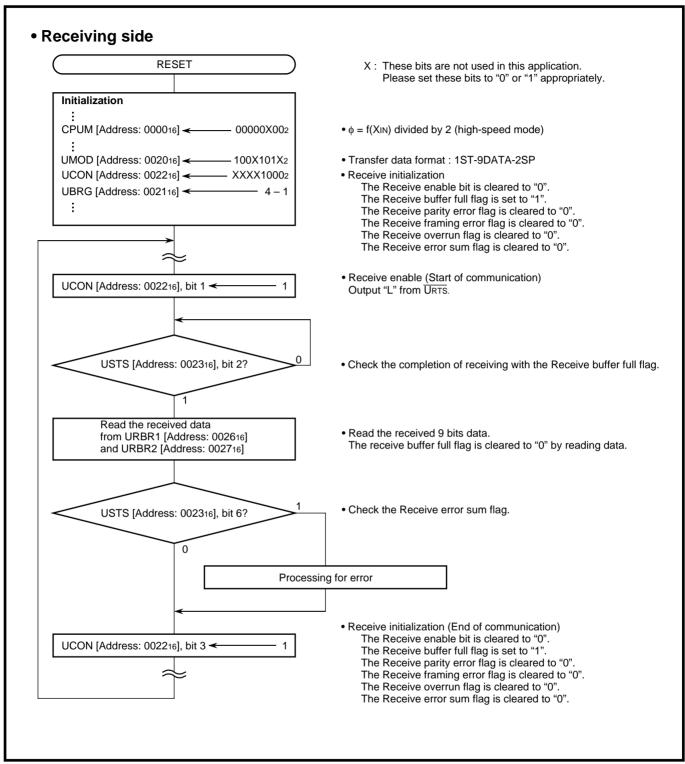

|        | 28 Block diagram of UART                                          |       |

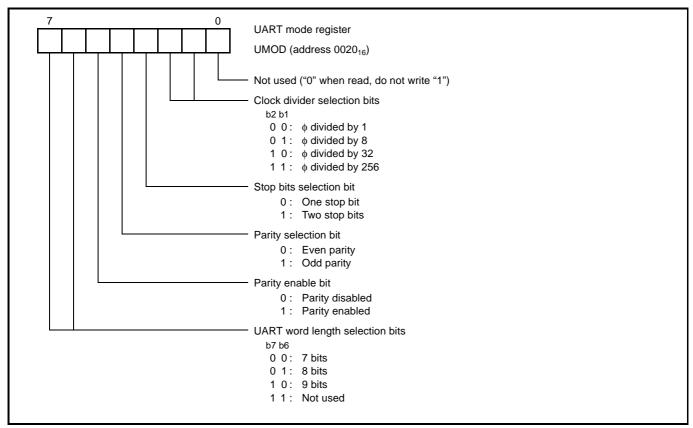

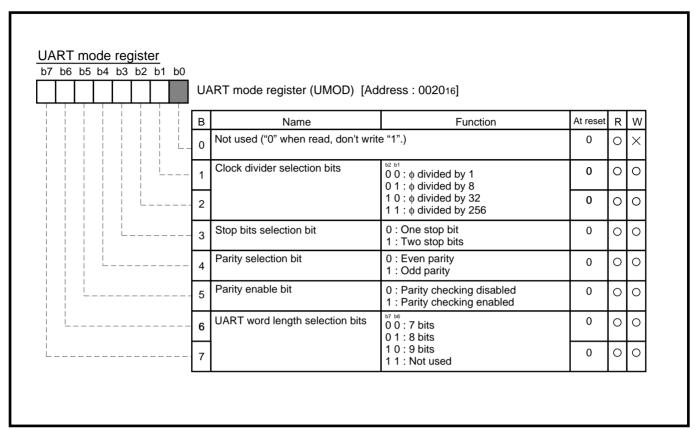

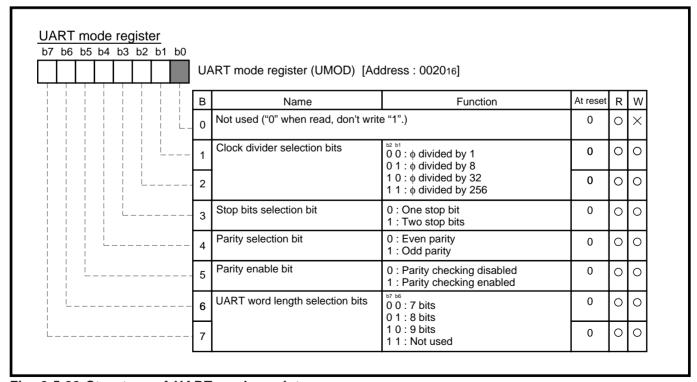

| Fig. 2 | 29 Structure of UART mode register                                | 1-31  |

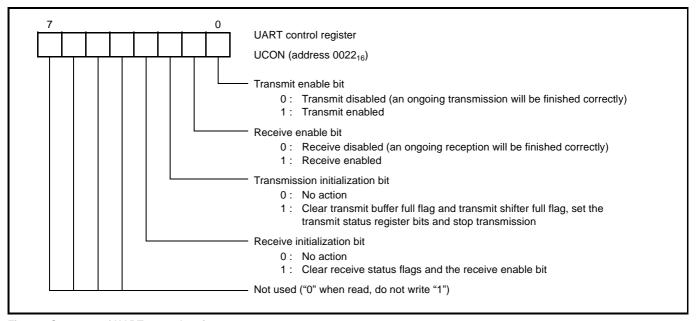

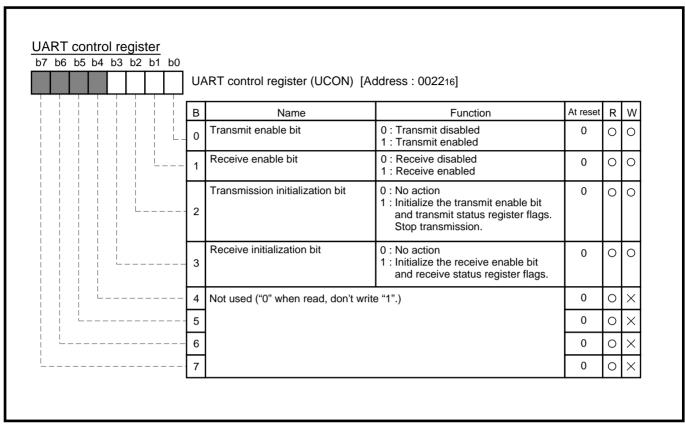

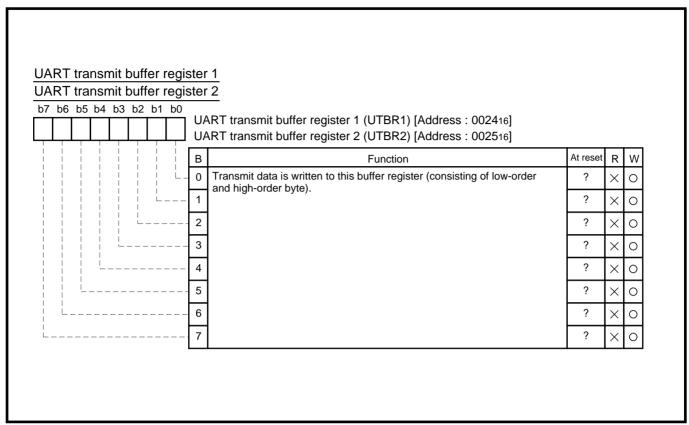

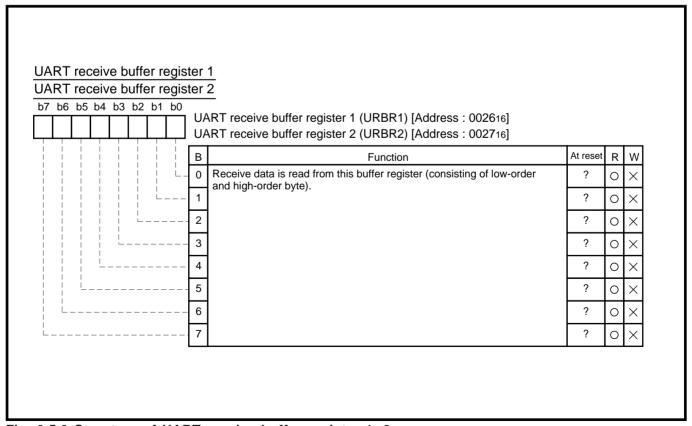

|        | 30 Structure of UART control register                             |       |

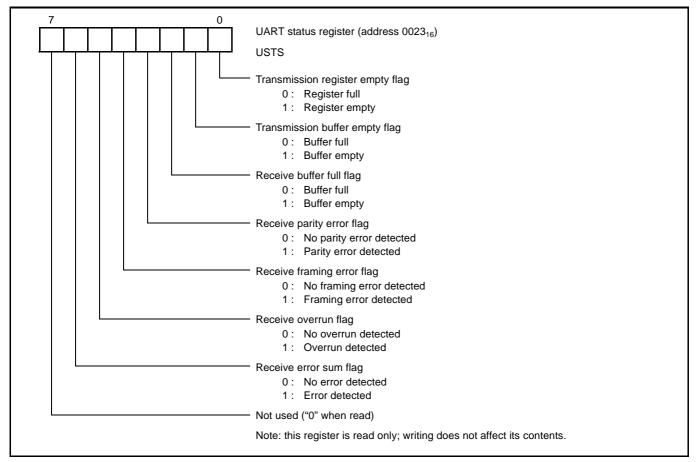

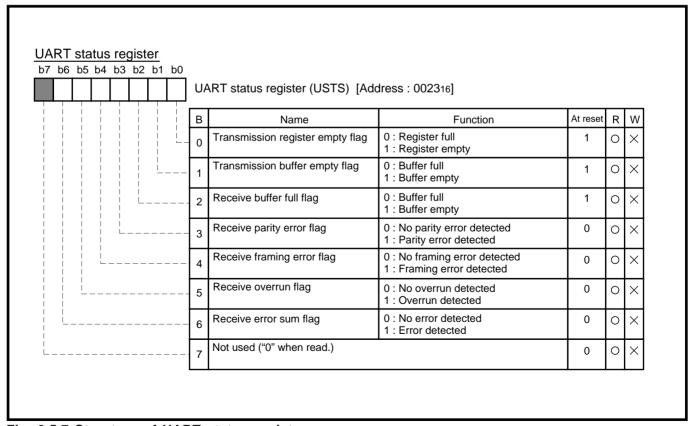

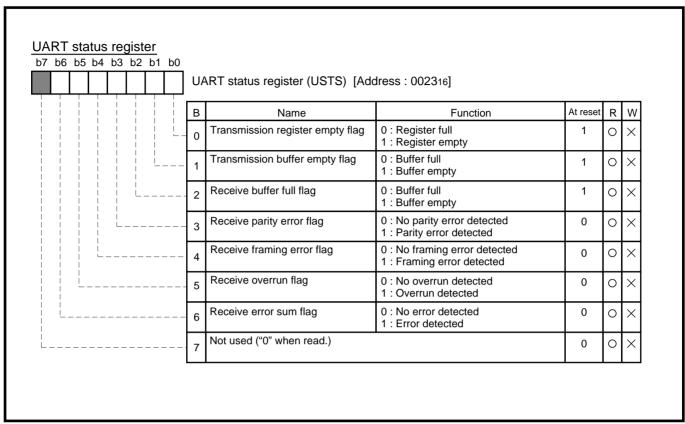

| Fig. 3 | 31 Structure of UART status register                              | 1-32  |

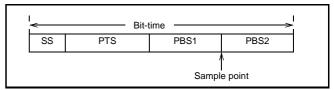

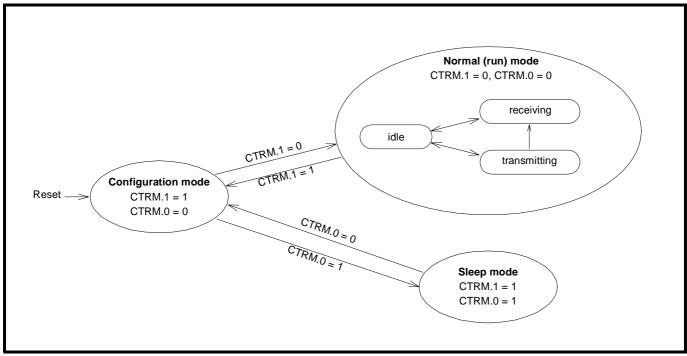

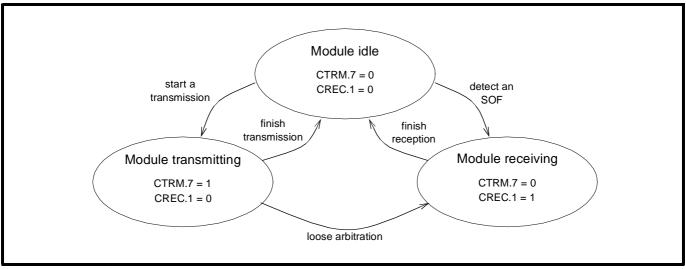

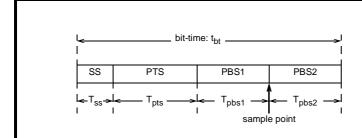

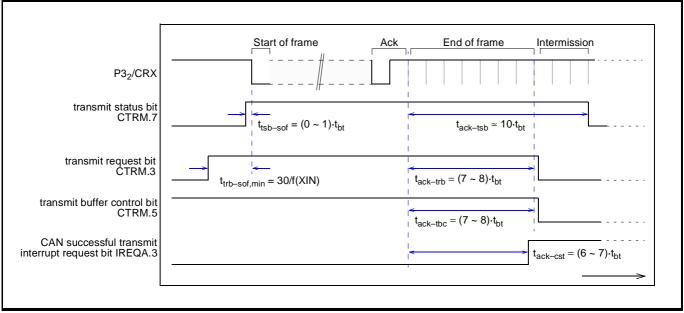

| Fig. 3 | 32 Bit time of CAN module                                         | 1-33  |

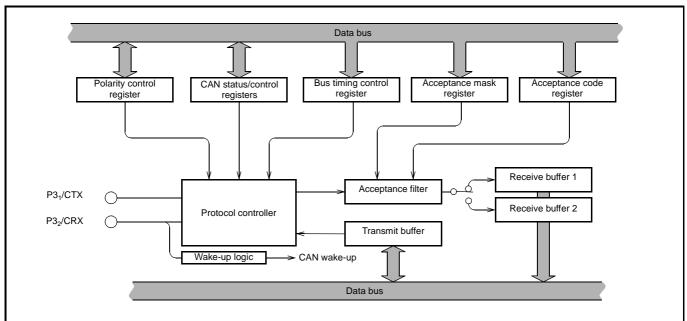

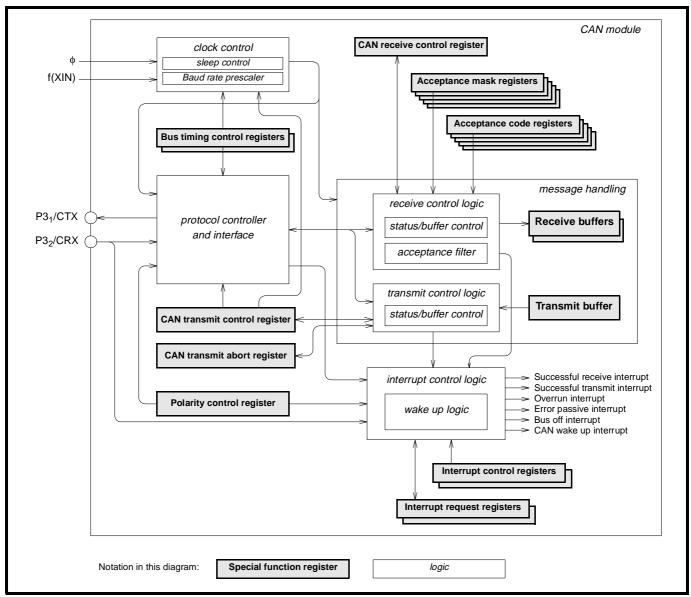

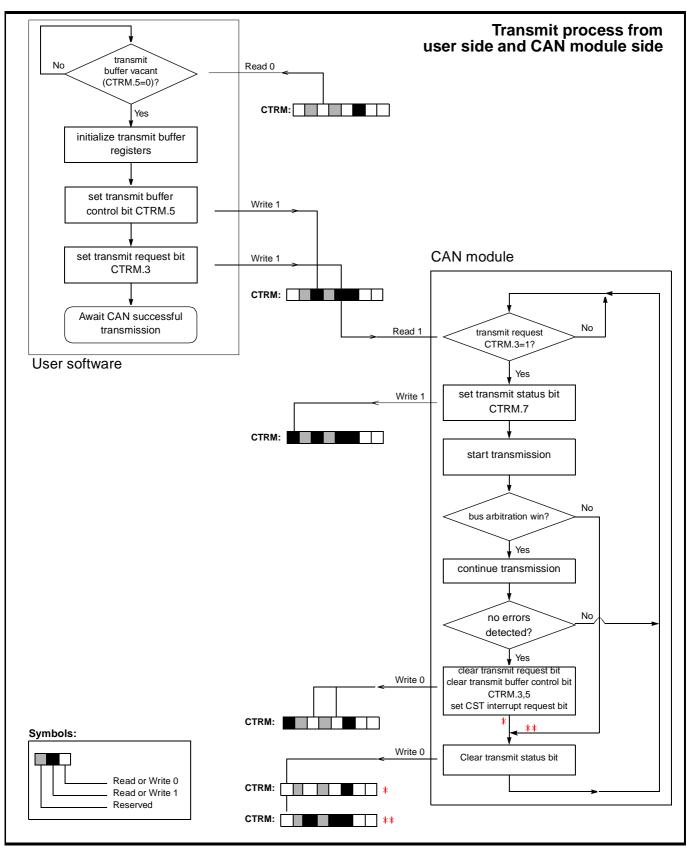

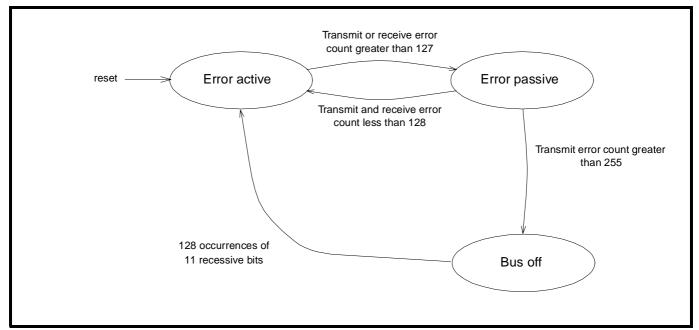

| Fig. 3 | 33 Block diagram of CAN module                                    | 1-33  |

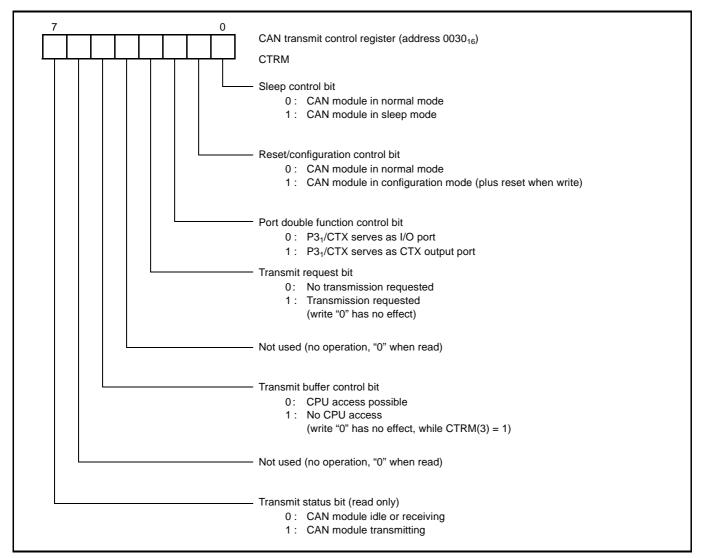

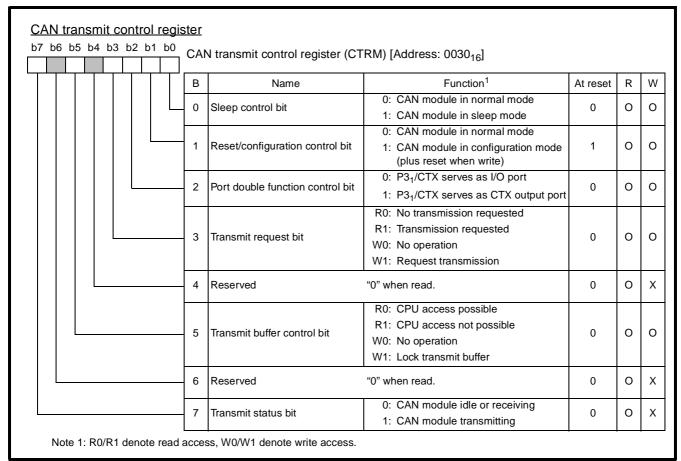

|        | 34 Structure of CAN transmit control register                     |       |

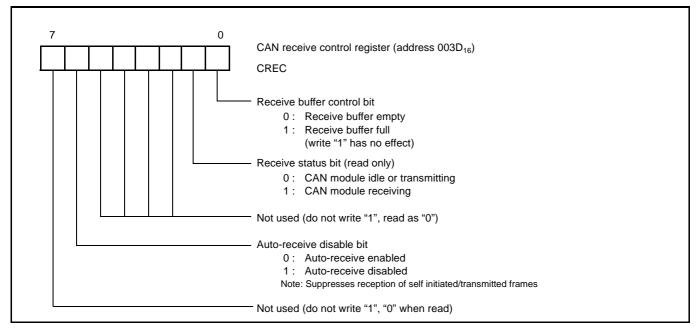

| Fig. 3 | 35 Structure of CAN receive control register                      | 1-34  |

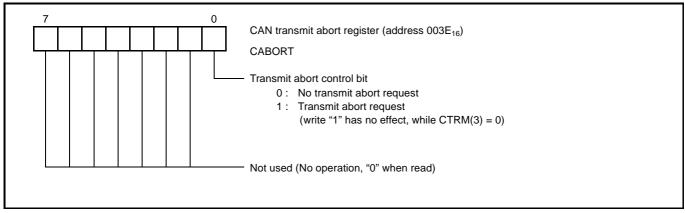

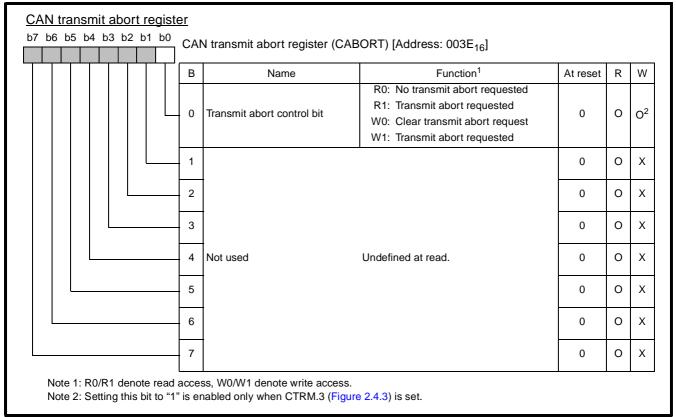

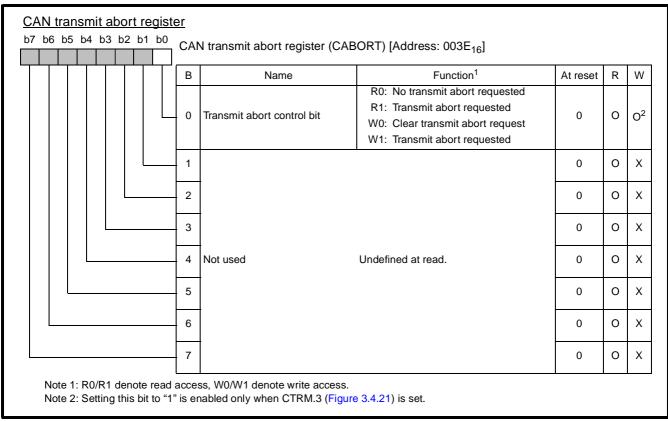

| Fig. 3 | 36 Structure of CAN transmit abort request register               | 1-35  |

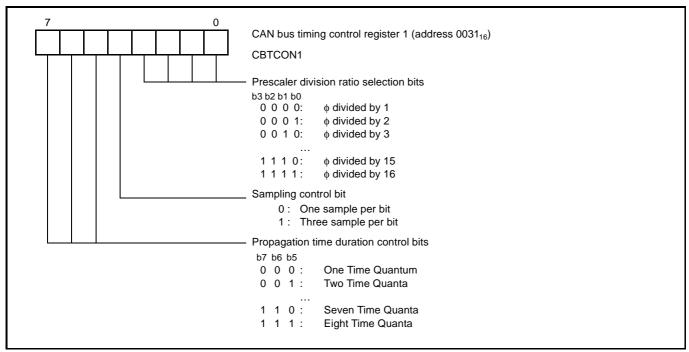

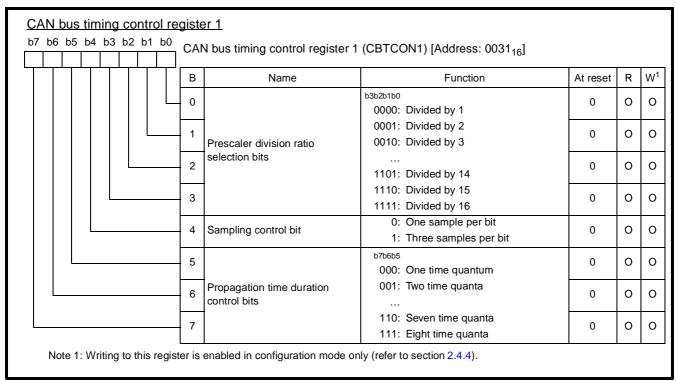

| Fig. 3 | 37 Structure of CAN bus timing control register 1                 | 1-35  |

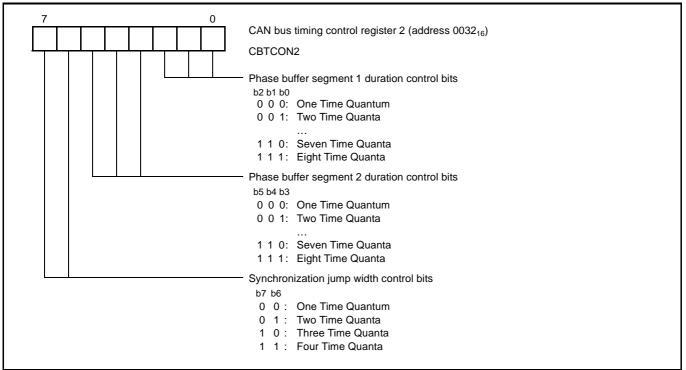

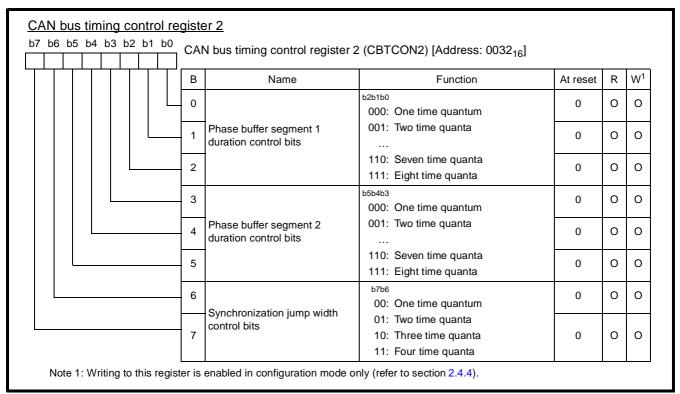

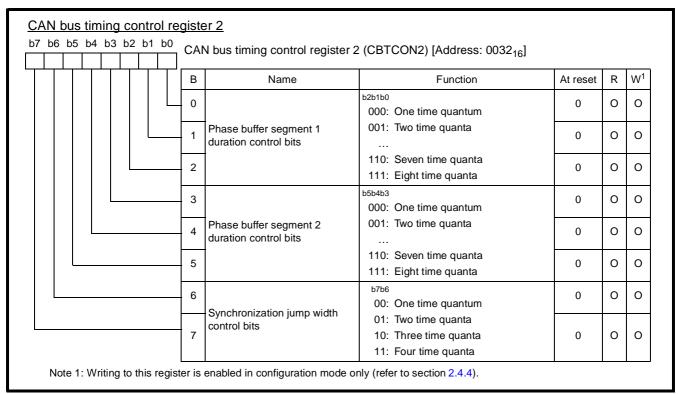

| Fig. 3 | 88 Structure of CAN bus timing control register 2                 | 1-36  |

| Fig. 3 | 39 Structure of CAN mask and code registers                       | 1-36  |

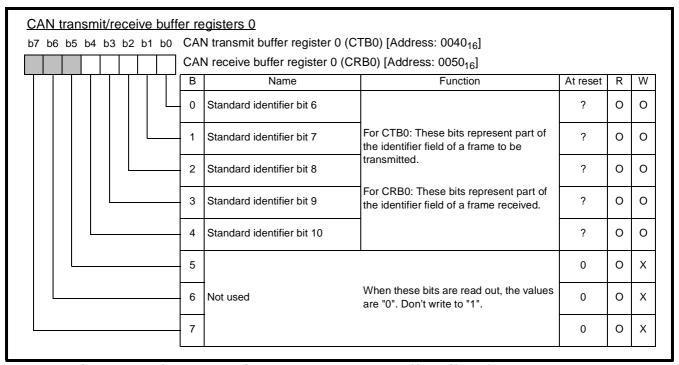

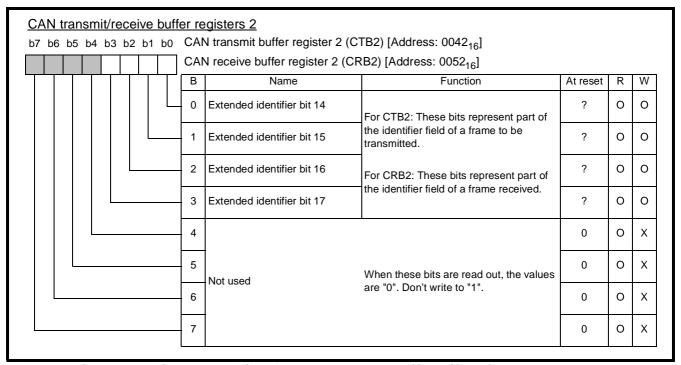

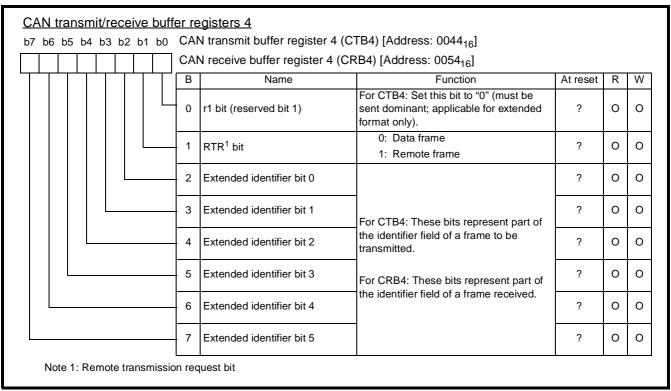

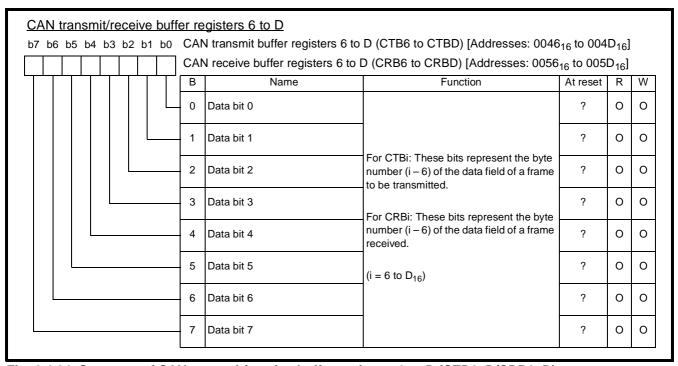

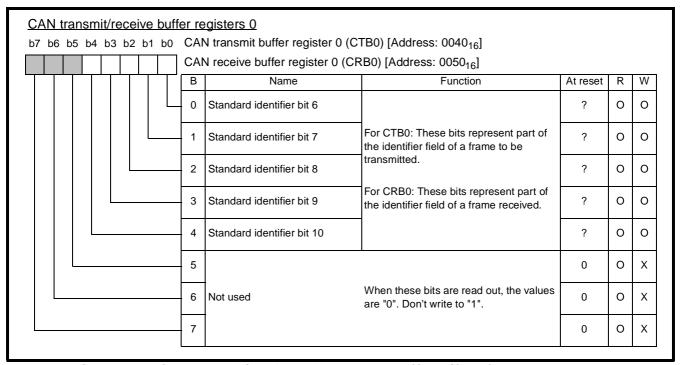

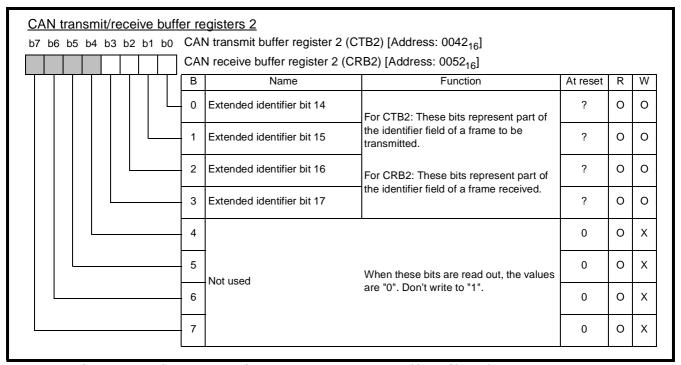

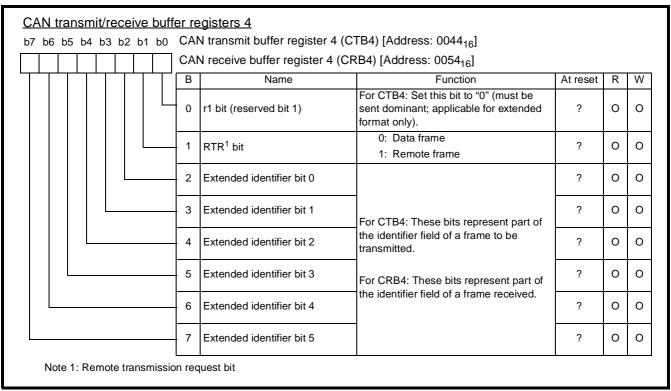

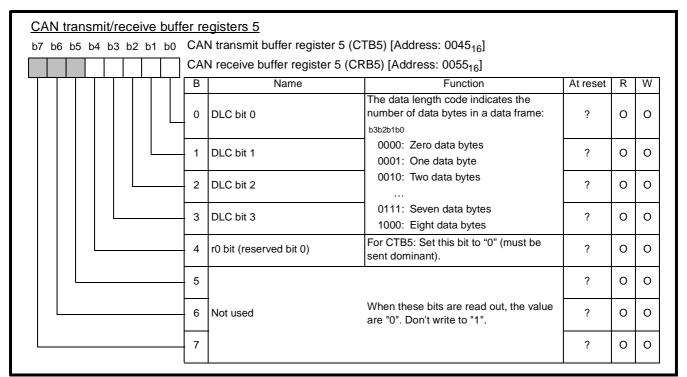

| Fig. 4 | 10 Structure of CAN transmission and reception buffer registers   | 1-37  |

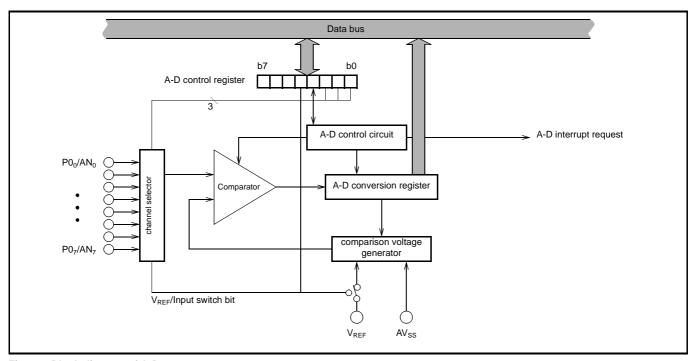

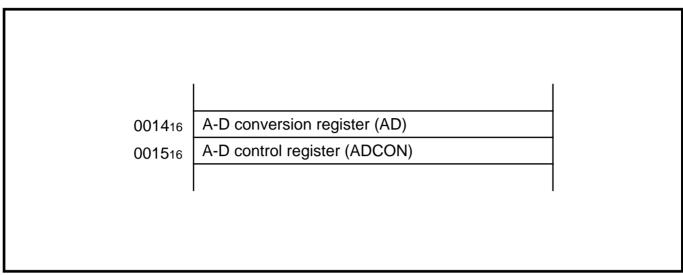

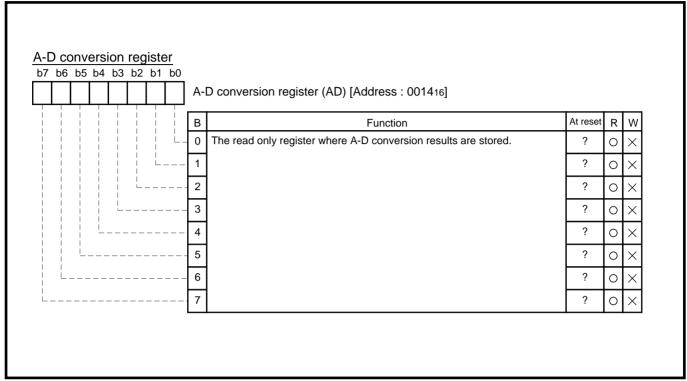

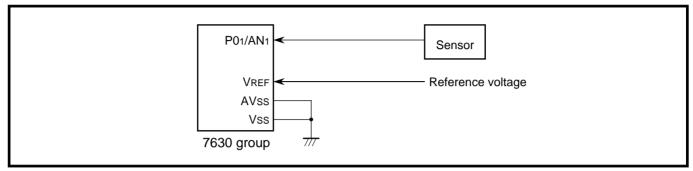

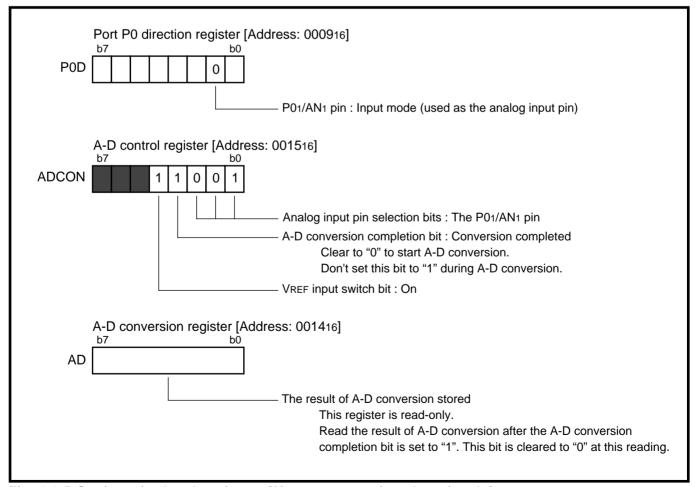

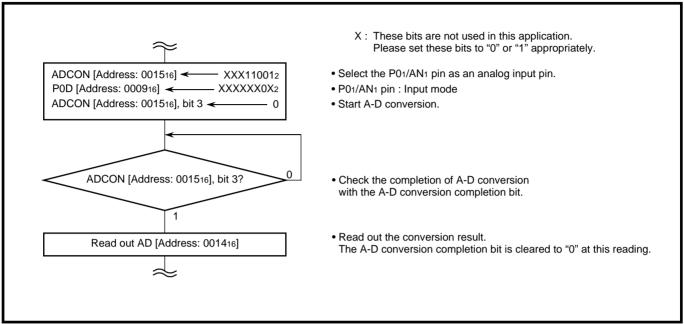

| Fig. 4 | 11 Block diagram of A-D converter                                 | 1-38  |

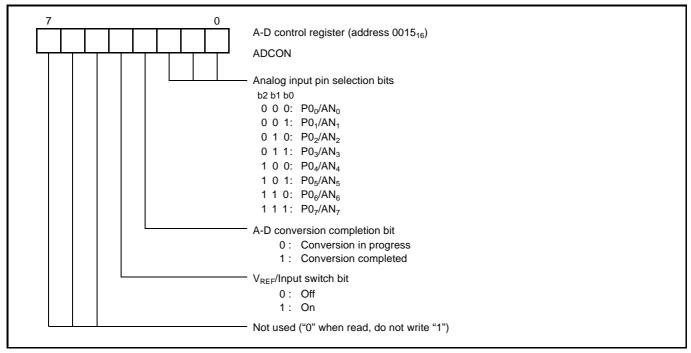

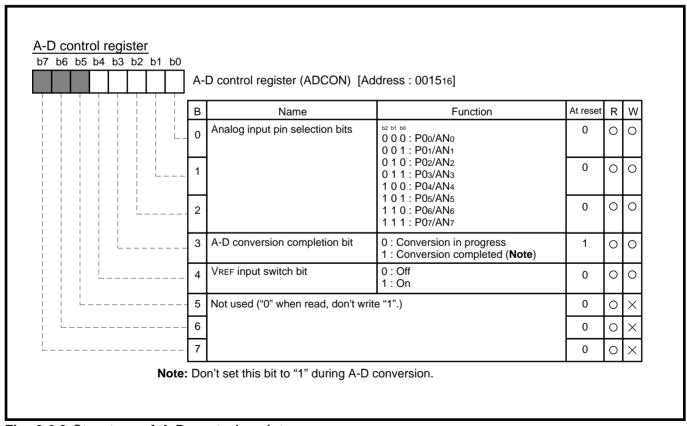

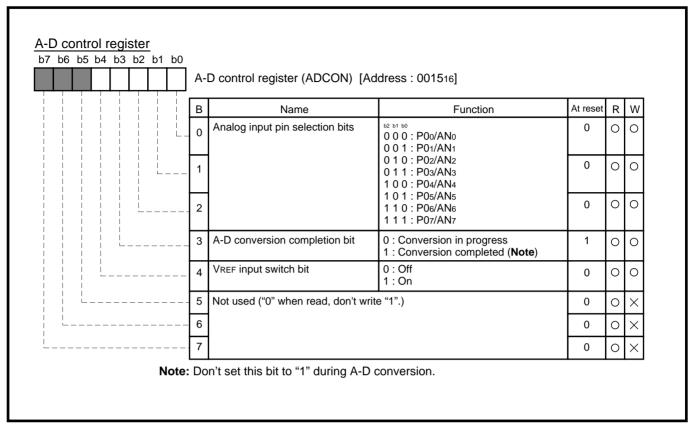

| Fig. 4 | 2 Structure of A-D control register                               | 1-39  |

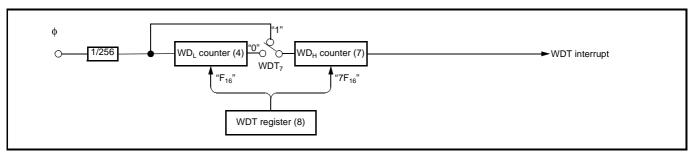

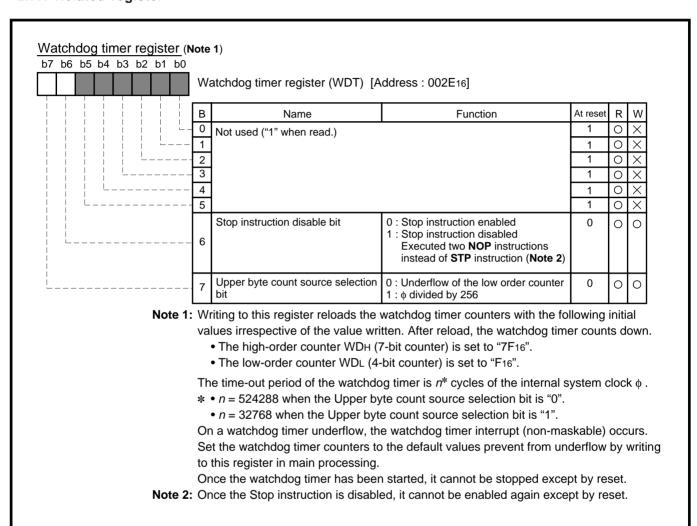

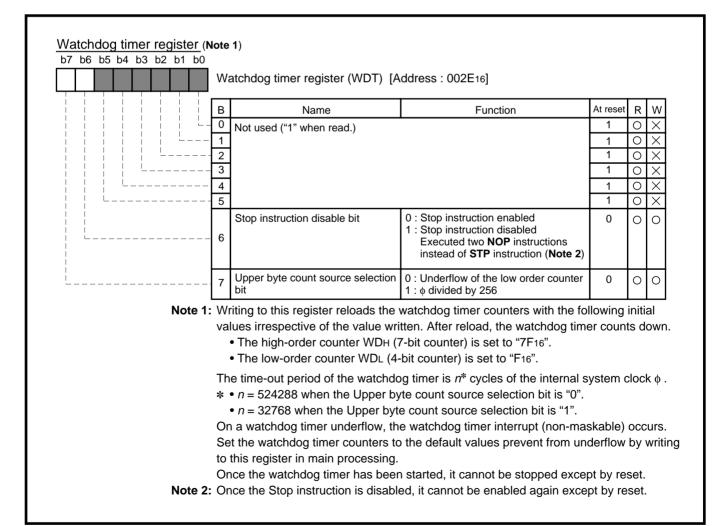

| Fig. 4 | 13 Block diagram of watchdog timer                                | 1-40  |

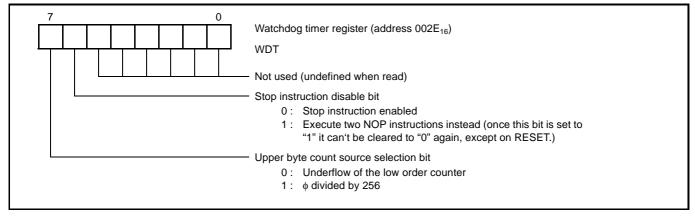

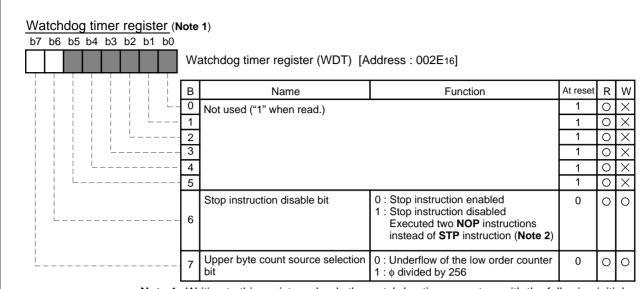

| Fig. 4 | 14 Structure of watchdog timer register                           | 1-40  |

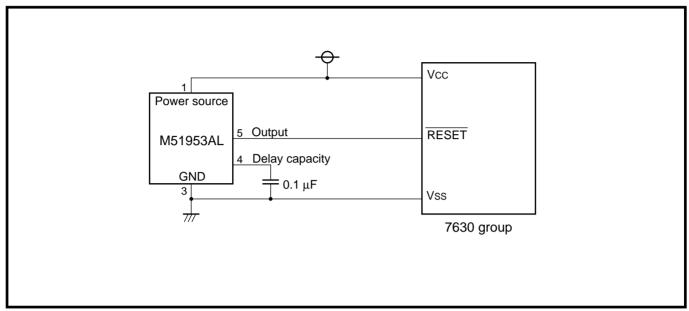

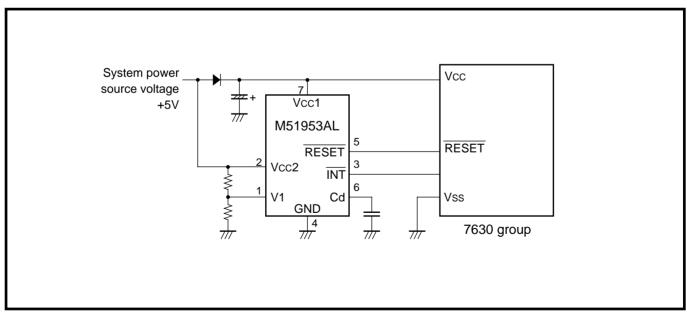

| Fig. 4 | 15 Example of reset circuit                                       | 1-41  |

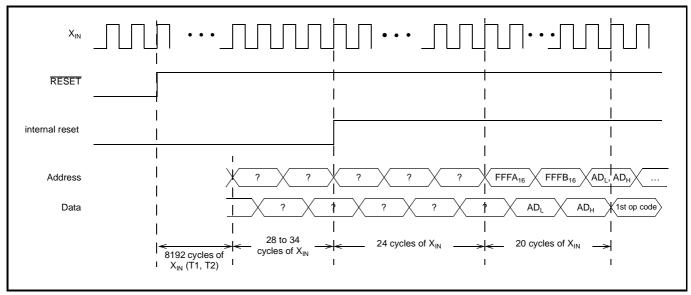

| Fig. 4 | 16 Reset sequence                                                 | 1-41  |

| Fig. 4 | 17 Internal status of microcomputer after reset                   | 1-42  |

| Fig. 48 Ceramic resonator circuit       |                                                                                                | 1-43 |

|-----------------------------------------|------------------------------------------------------------------------------------------------|------|

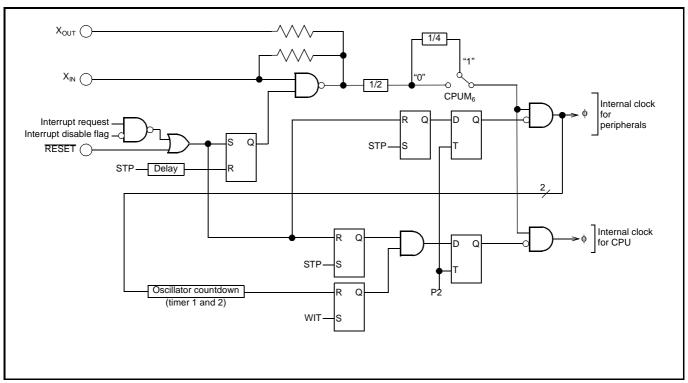

| Fig. 49 Block diagram of clock gen      | erating circuit                                                                                | 1-43 |

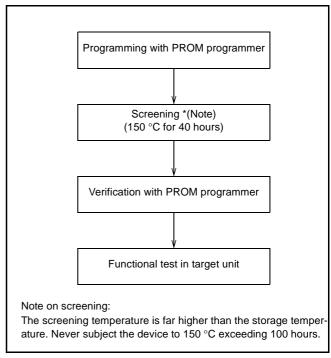

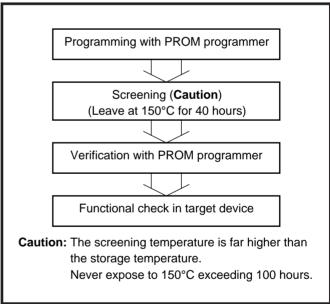

| Fig. 50 Programming and testing o       | f One Time PROM version                                                                        | 1-44 |

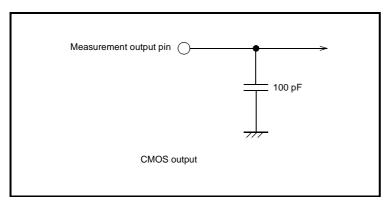

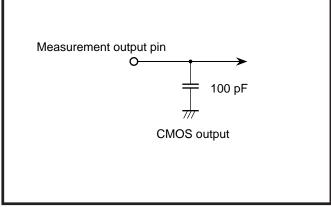

| Fig. 51 Circuit for measuring outpu     | t switching characteristics                                                                    | 1-49 |

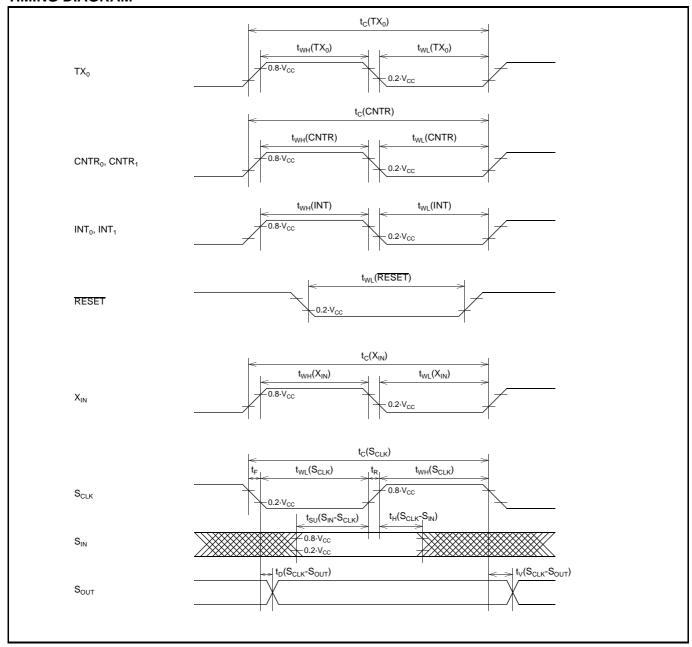

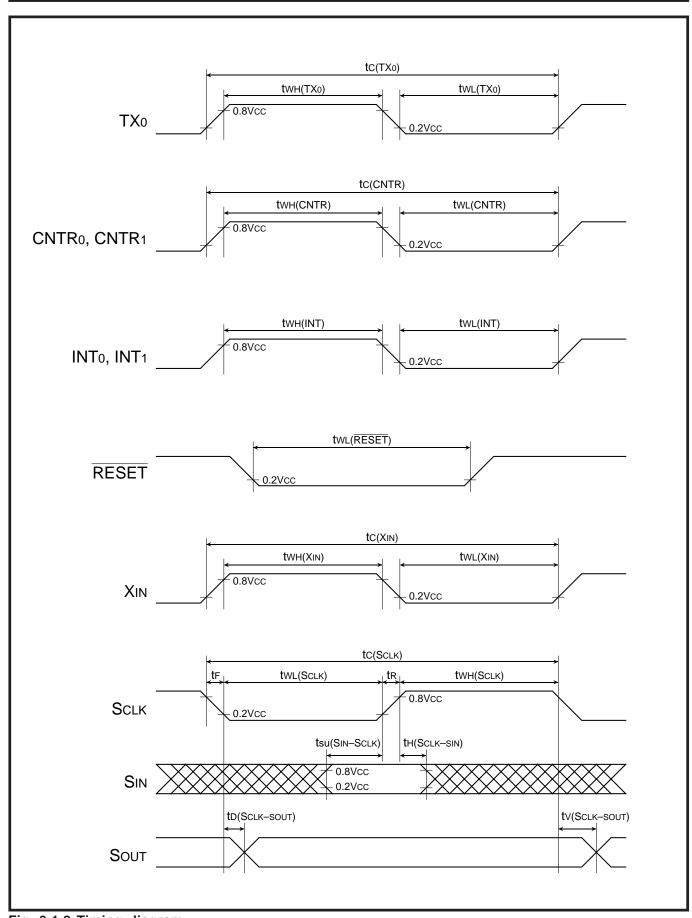

| Fig. 52 Timing diagram                  | -                                                                                              | 1-50 |

| OUARTER A ARRUGATION                    |                                                                                                |      |

| CHAPTER 2. APPLICATION                  |                                                                                                |      |

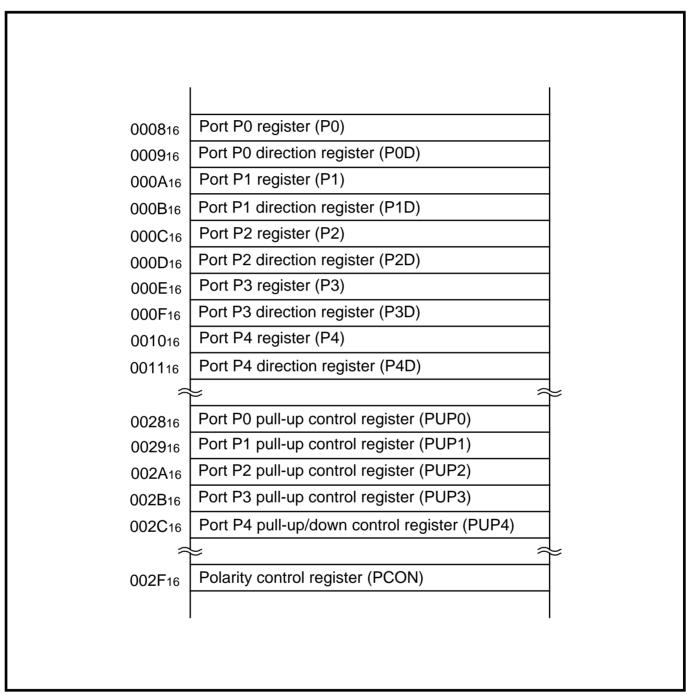

| Fig. 2.1.1 Memory map of I/O port       | related registers                                                                              | 2-2  |

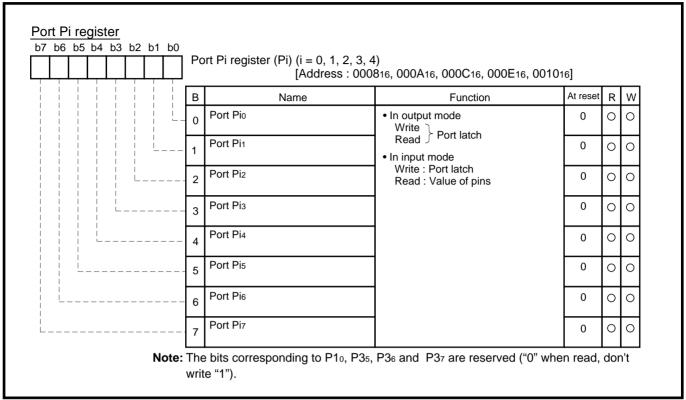

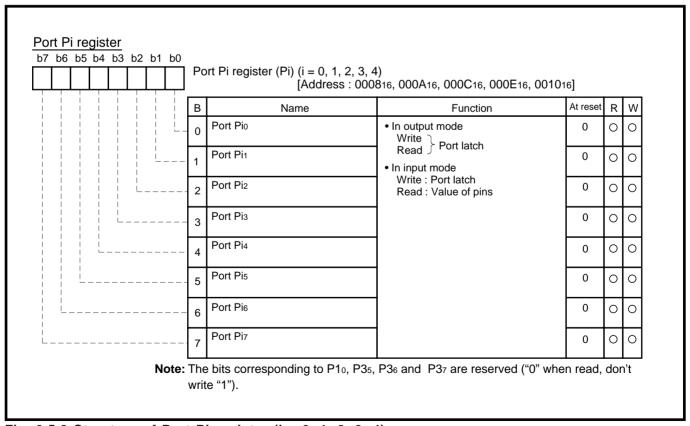

|                                         | ster (i = 0, 1, 2, 3, 4)                                                                       |      |

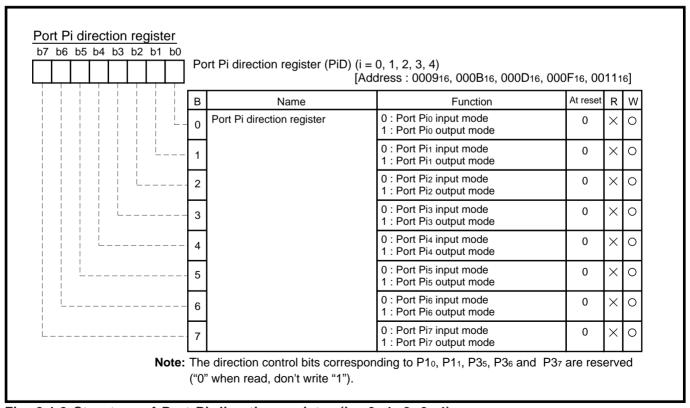

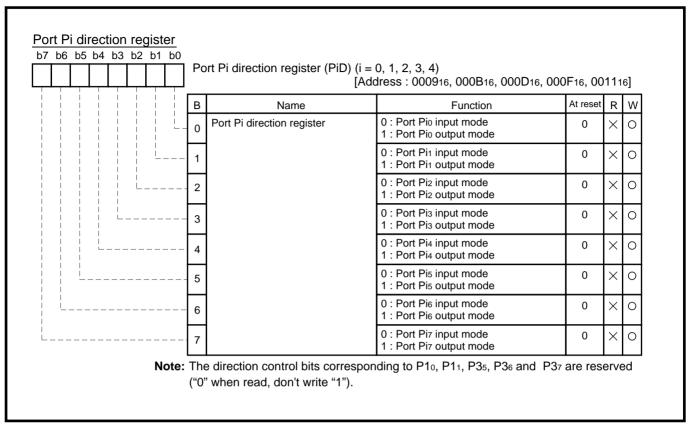

|                                         | ction register (i = 0, 1, 2, 3, 4)                                                             |      |

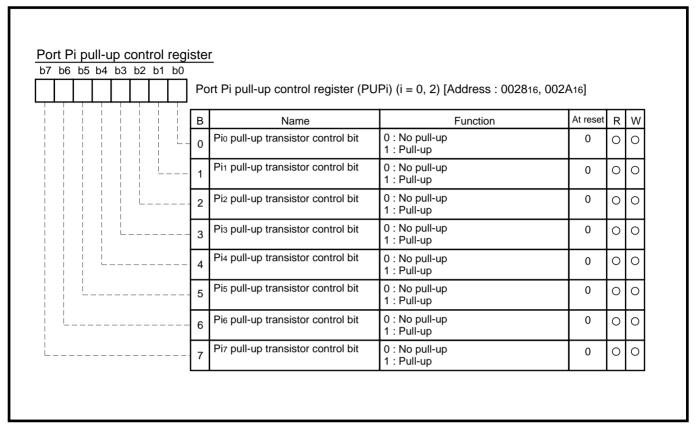

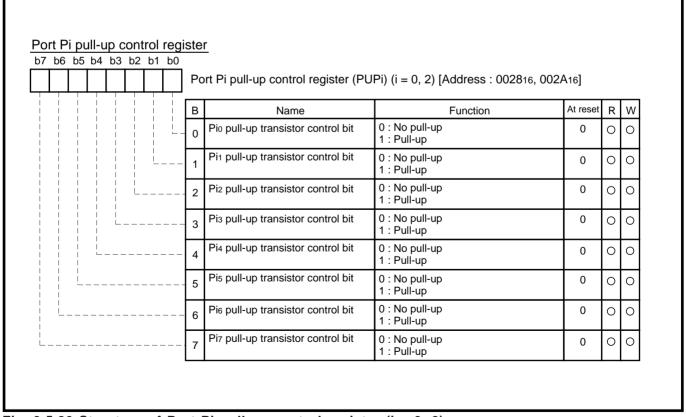

| Fig. 2.1.4 Structure of Port Pi pull-   | up register (i = 0, 2)                                                                         | 2-4  |

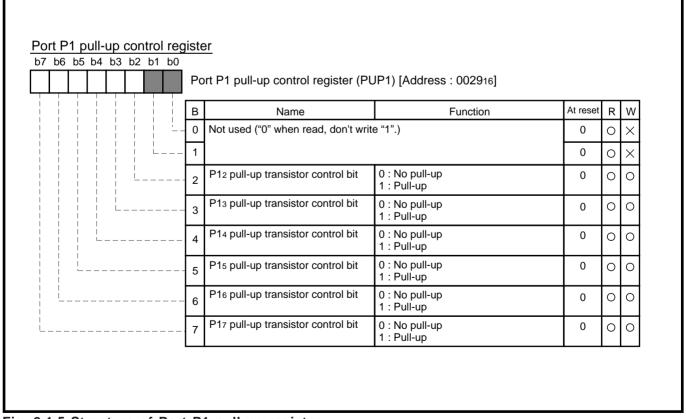

| Fig. 2.1.5 Structure of Port P1 pull-   | -up register                                                                                   | 2-4  |

| Fig. 2.1.6 Structure of Port P3 pull-   | -up control register                                                                           | 2-5  |

| Fig. 2.1.7 Structure of Port P4 pull-   | -up/down control register                                                                      | 2-5  |

| Fig. 2.1.8 Structure of Porarity con    | trol register                                                                                  | 2-6  |

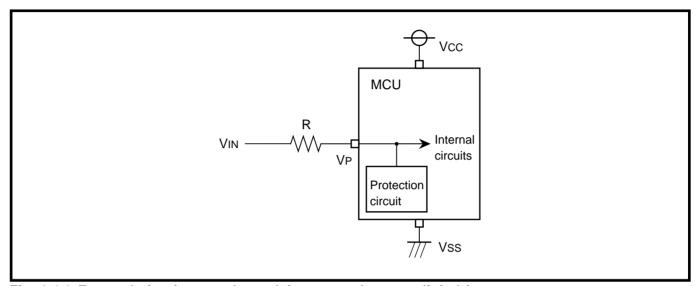

| Fig. 2.1.9 External circuit example     | applying overvoltage to digital inputs                                                         | 2-7  |

| Fig. 2.2.1 Memory map of interrupt      | related registers                                                                              | 2-9  |

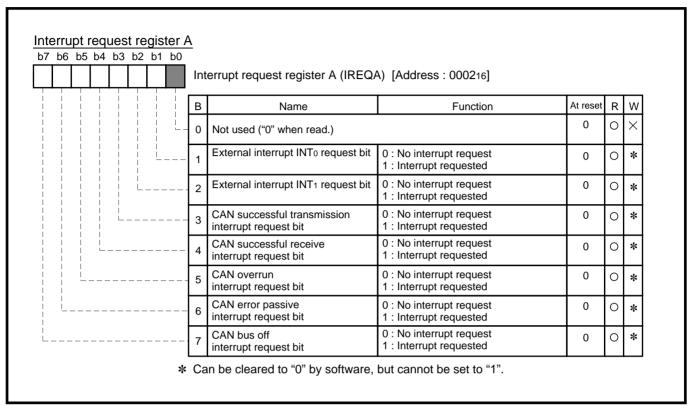

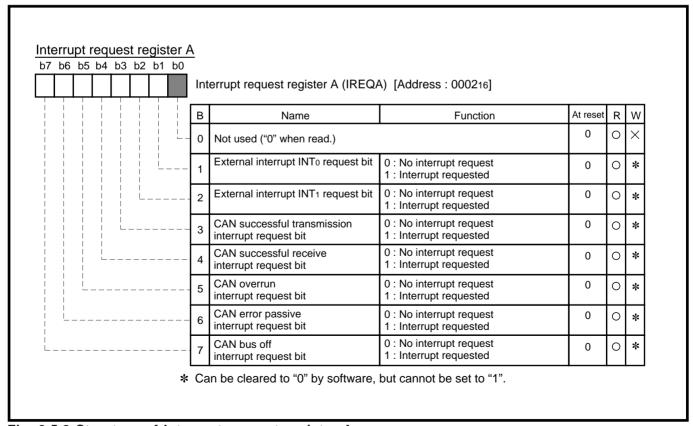

| -                                       | uest register A                                                                                |      |

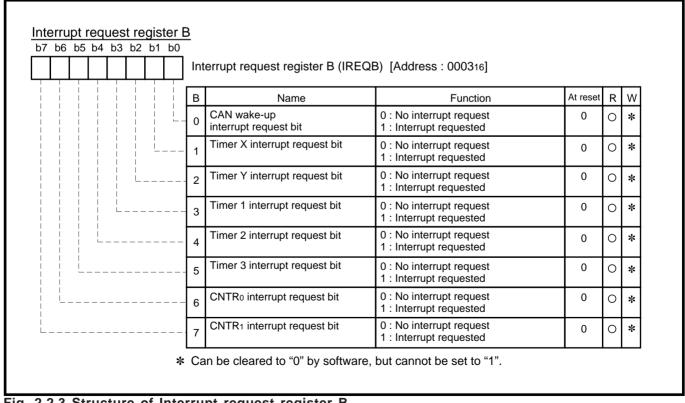

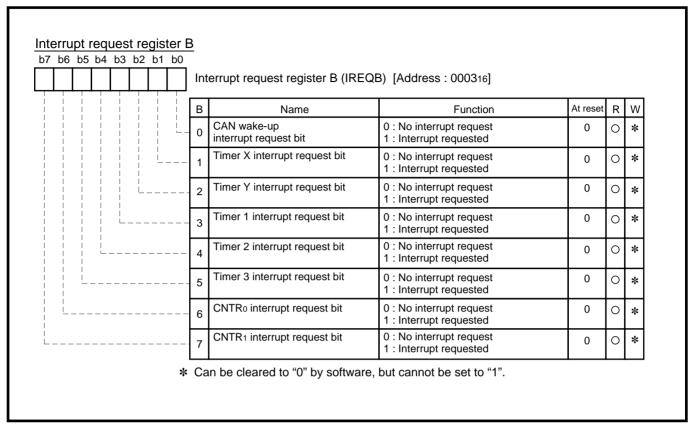

| •                                       | uest register B                                                                                |      |

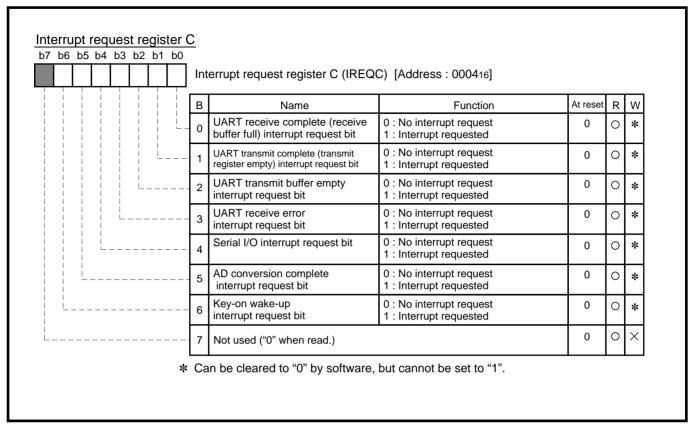

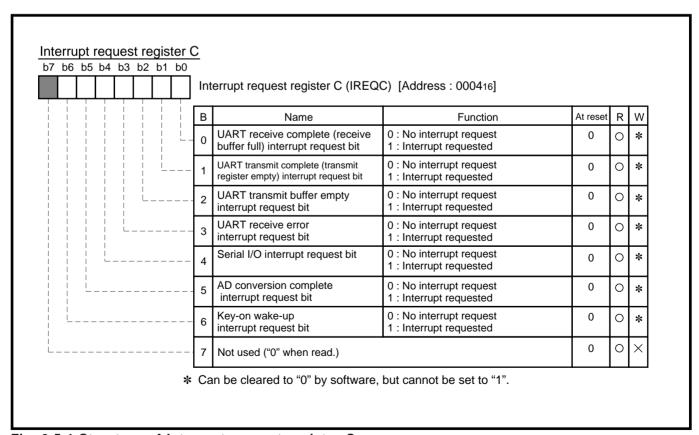

| •                                       | uest register C                                                                                |      |

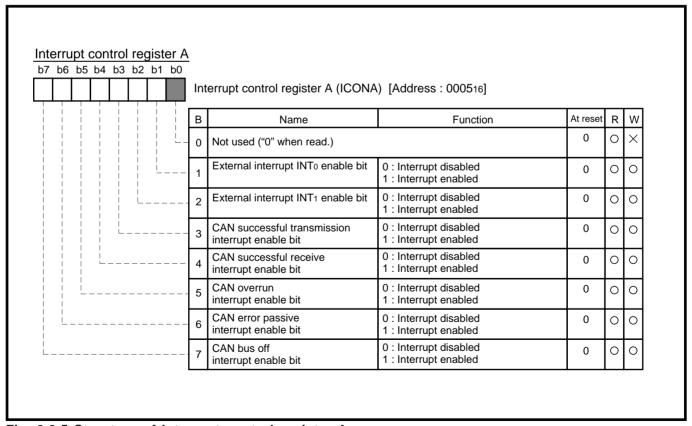

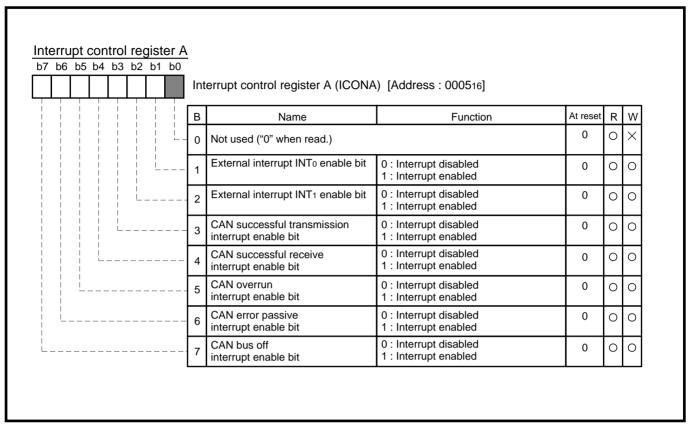

|                                         | ntrol register A                                                                               |      |

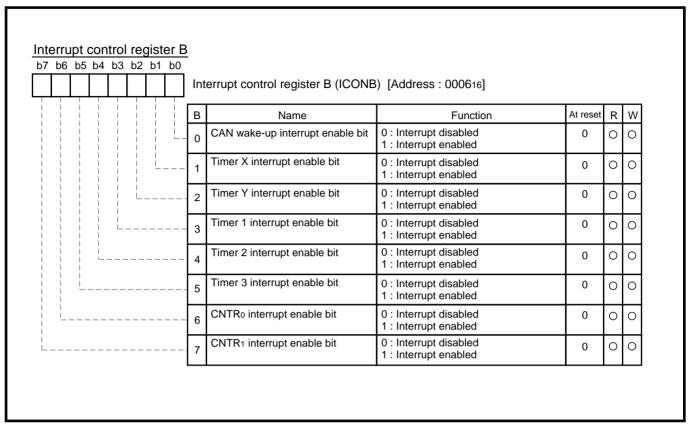

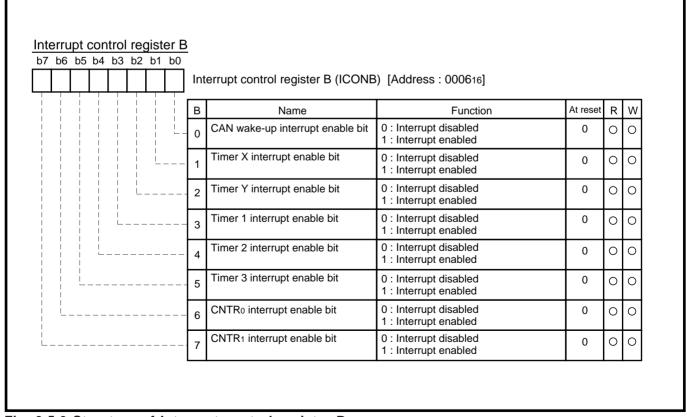

|                                         | ntrol register B                                                                               |      |

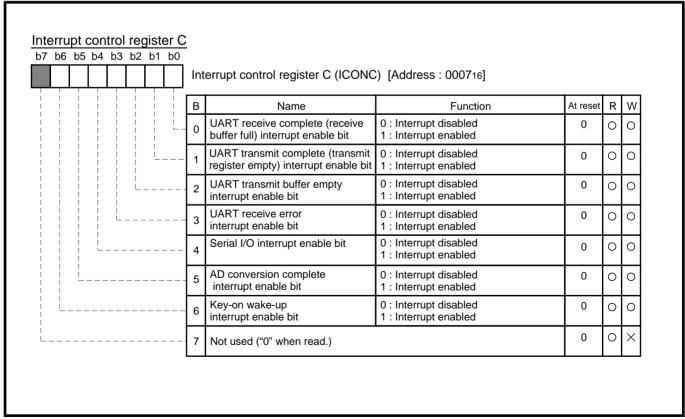

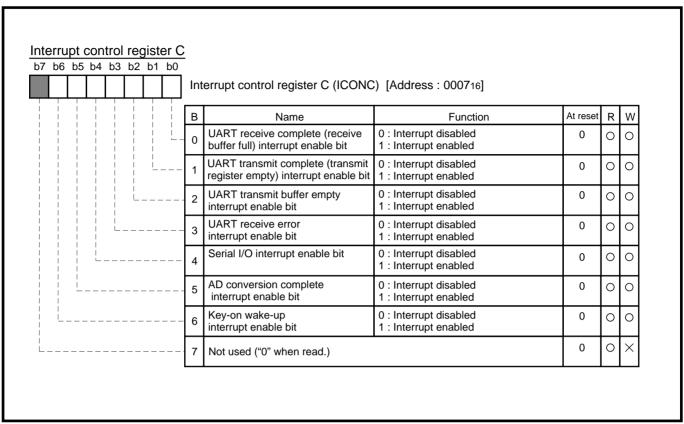

|                                         | ntrol register C                                                                               |      |

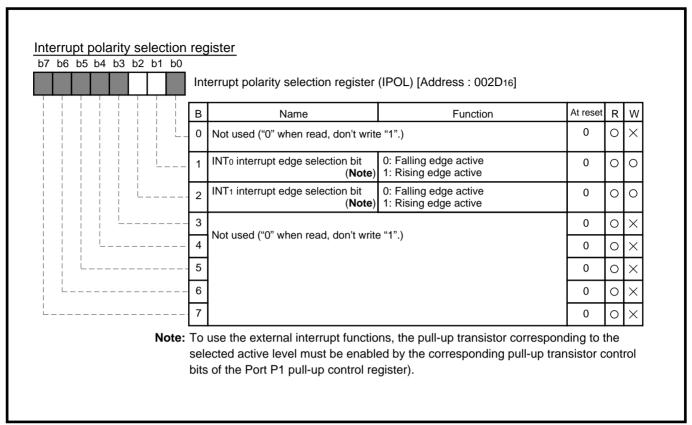

|                                         | arity selection register                                                                       |      |

|                                         | rol register                                                                                   |      |

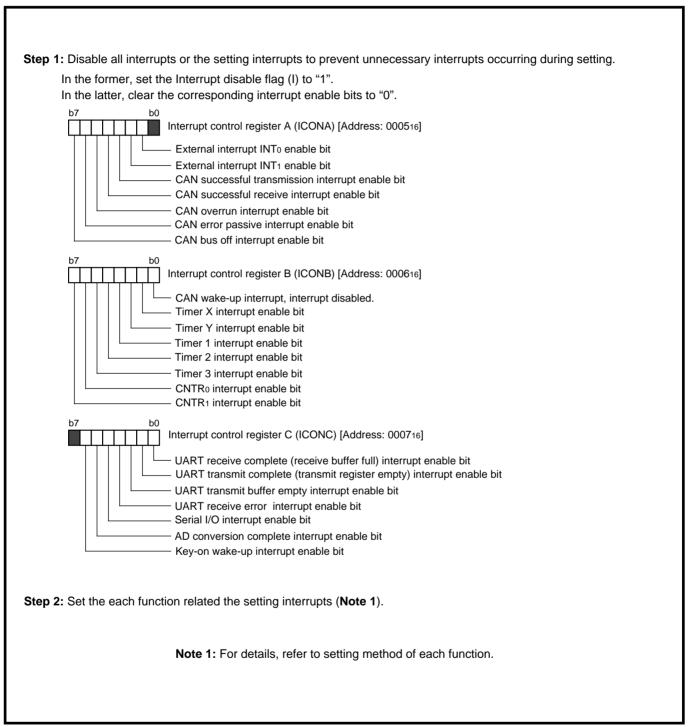

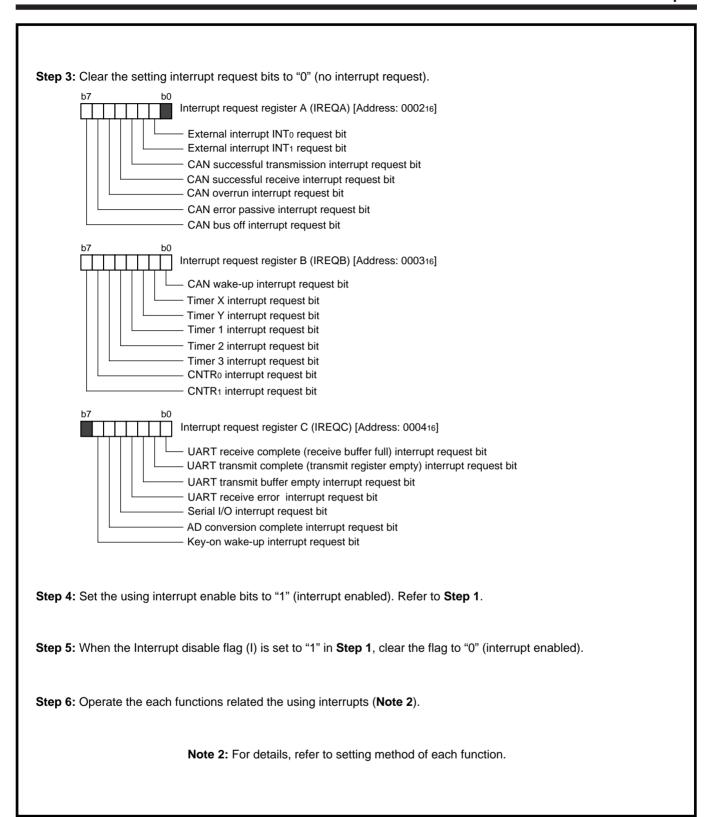

| • • • • • • • • • • • • • • • • • • • • | l (1)                                                                                          |      |

|                                         | (2)                                                                                            |      |

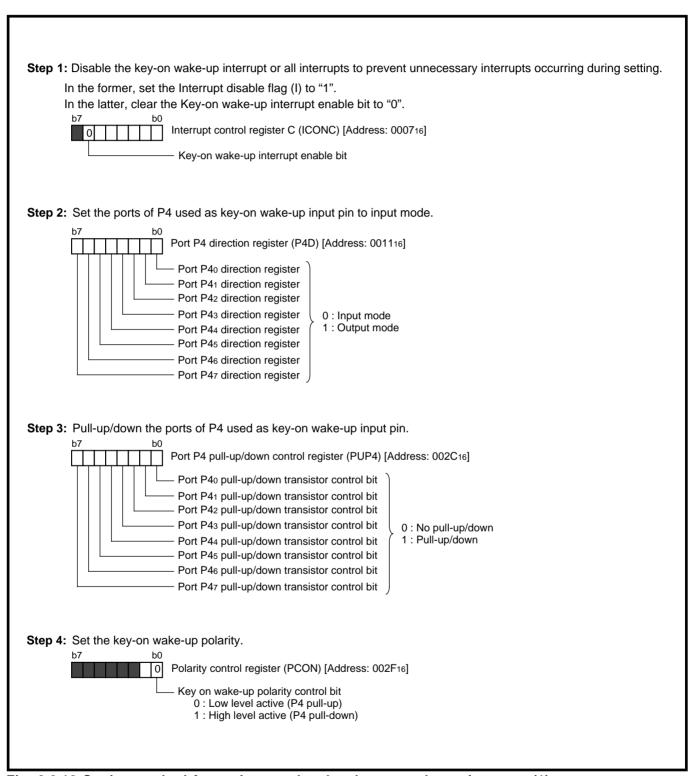

|                                         | sters related to key-on wake-up interrupt (1)<br>sters related to key-on wake-up interrupt (2) |      |

|                                         | ated registers                                                                                 |      |

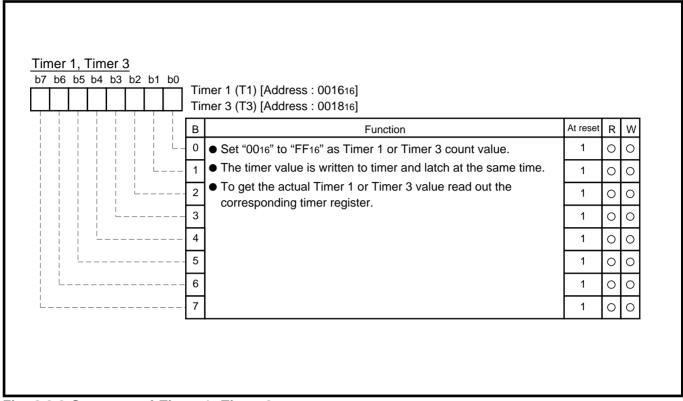

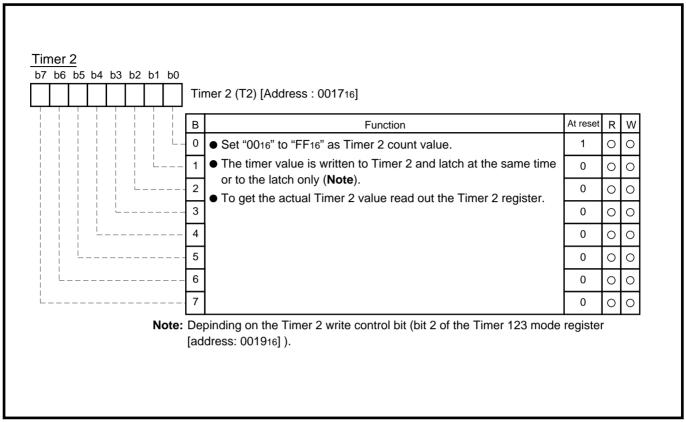

| - · · · · · · · · · · · · · · · · · · · | ner 3                                                                                          |      |

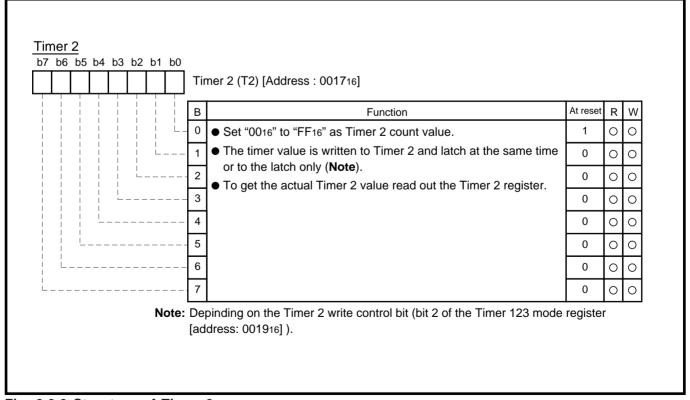

| _                                       |                                                                                                |      |

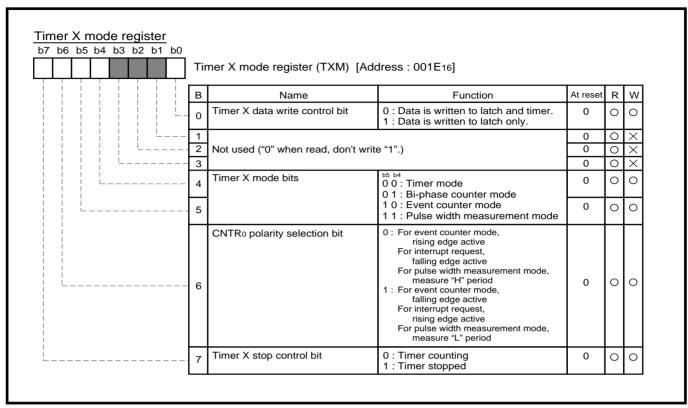

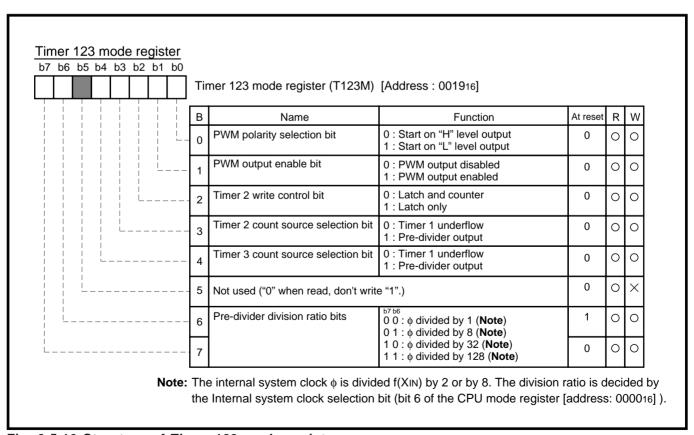

| <del>_</del>                            | node register                                                                                  |      |

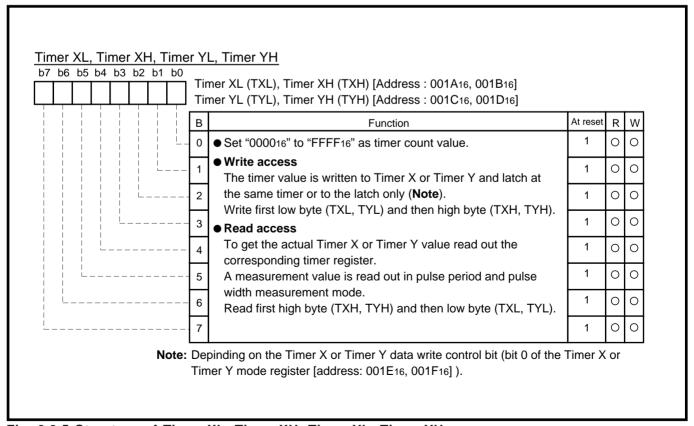

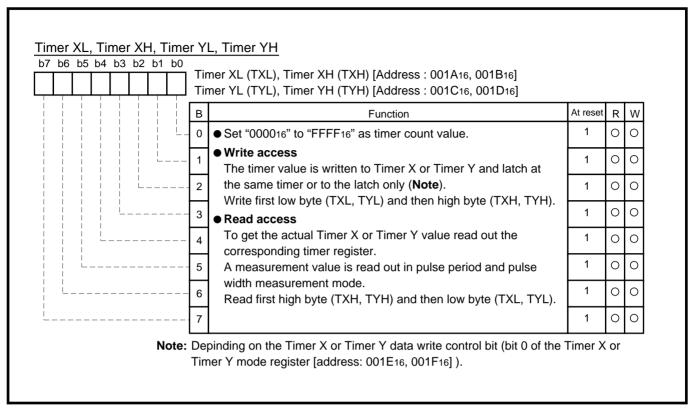

| •                                       | imer XH, Timer YL, Timer YH                                                                    |      |

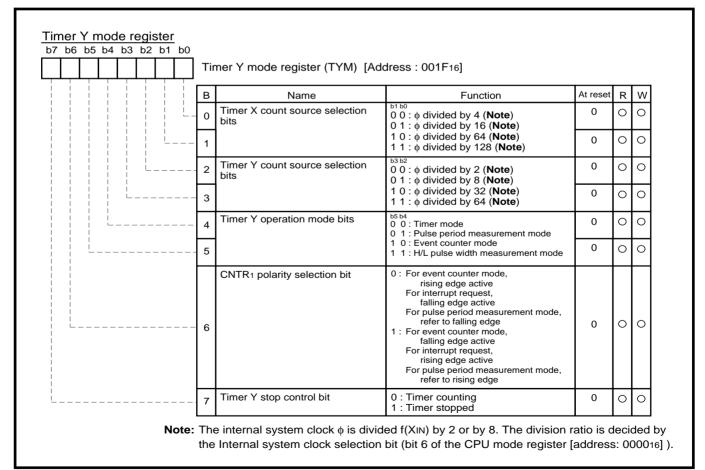

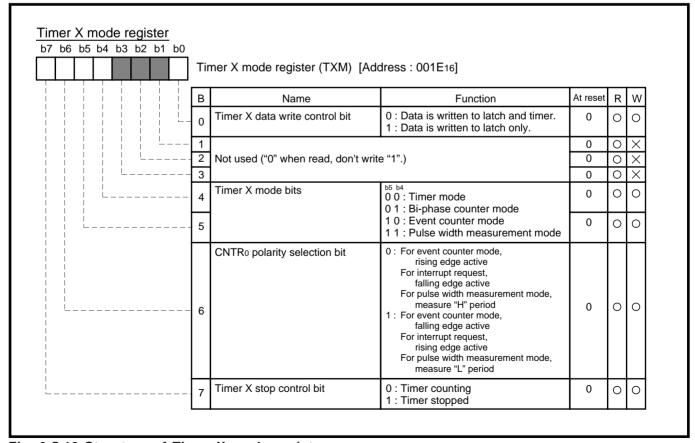

|                                         | de register                                                                                    |      |

| _                                       | de register                                                                                    |      |

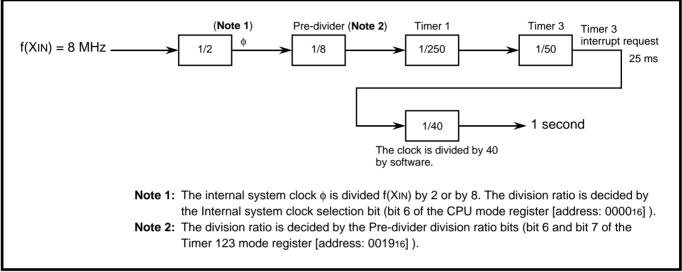

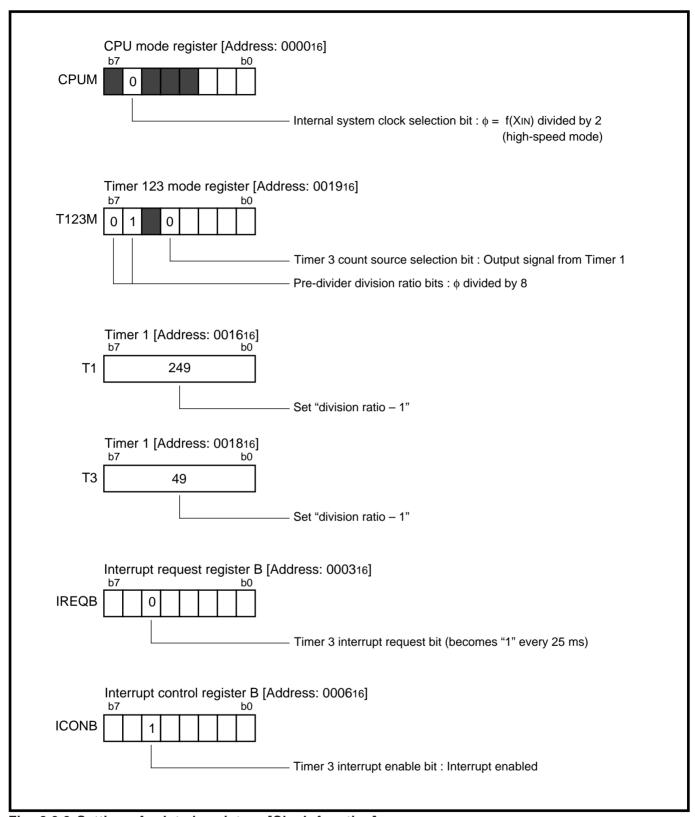

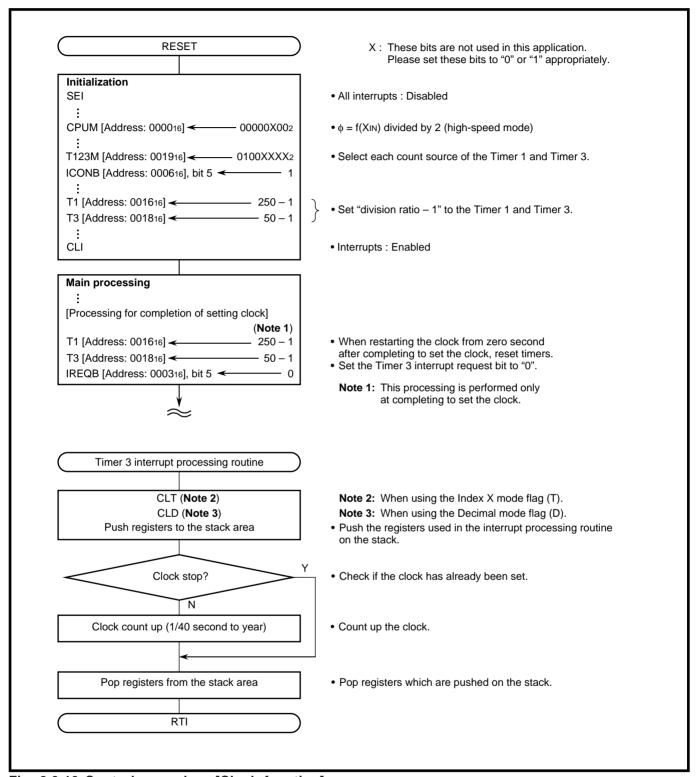

|                                         | ivision ratios [Clock function]                                                                |      |

|                                         | rs [Clock function]                                                                            |      |

|                                         | k function]                                                                                    |      |

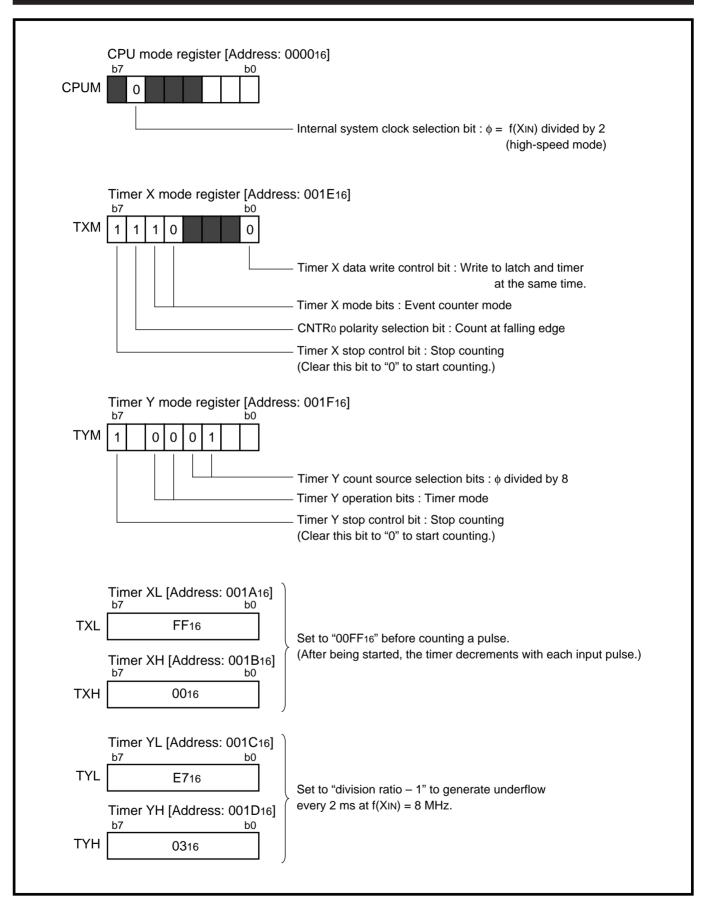

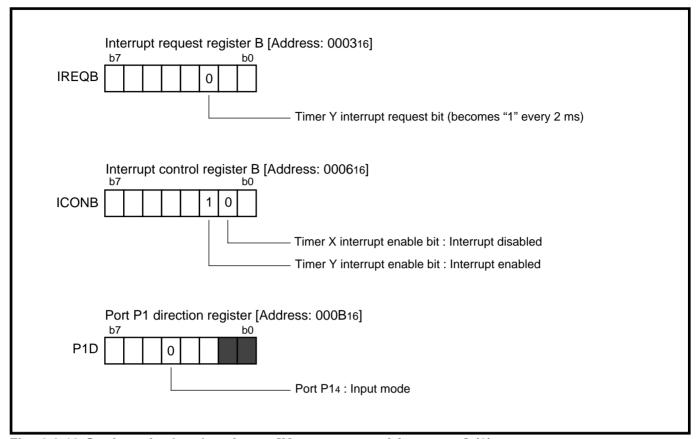

|                                         | input pulse exists                                                                             |      |

| Fig. 2.3.12 Setting of related regist   | ers [Measurement of frequency] (1)                                                             | 2-27 |

| Fig. 2.3.13 Setting of related regist   | ers [Measurement of frequency] (2)                                                             | 2-28 |

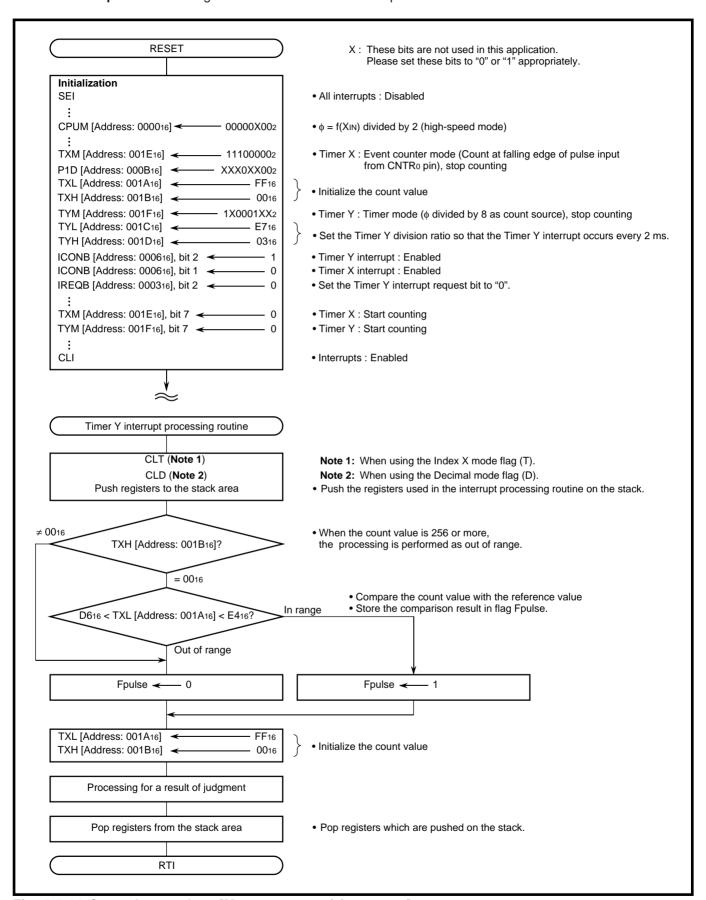

| Fig. 2.3.14 Control procedure [Mea      | surement of frequency]                                                                         | 2-29 |

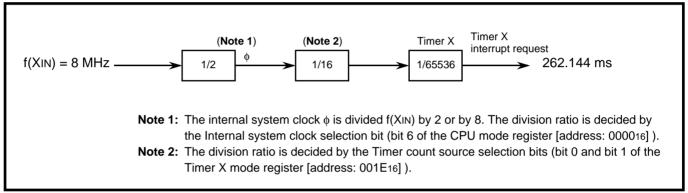

| Fig. 2.3.15 Timer connection and d      | livision ratios [Measurement of pulse width]                                                   | 2-30 |

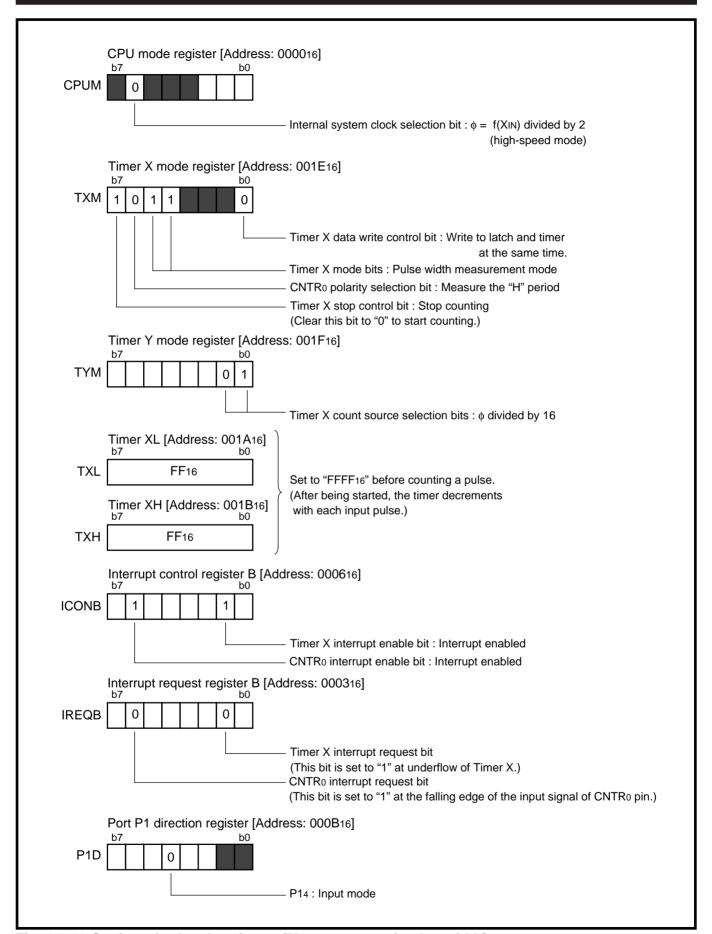

| •                                       | ers [Measurement of pulse width]                                                               |      |

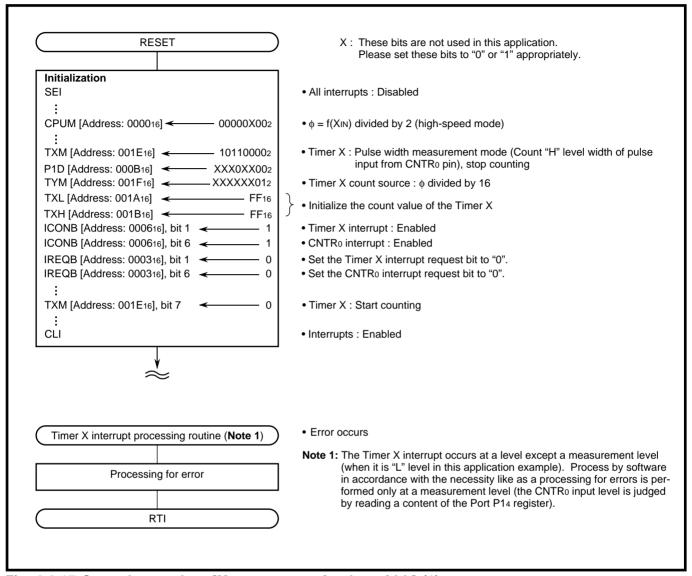

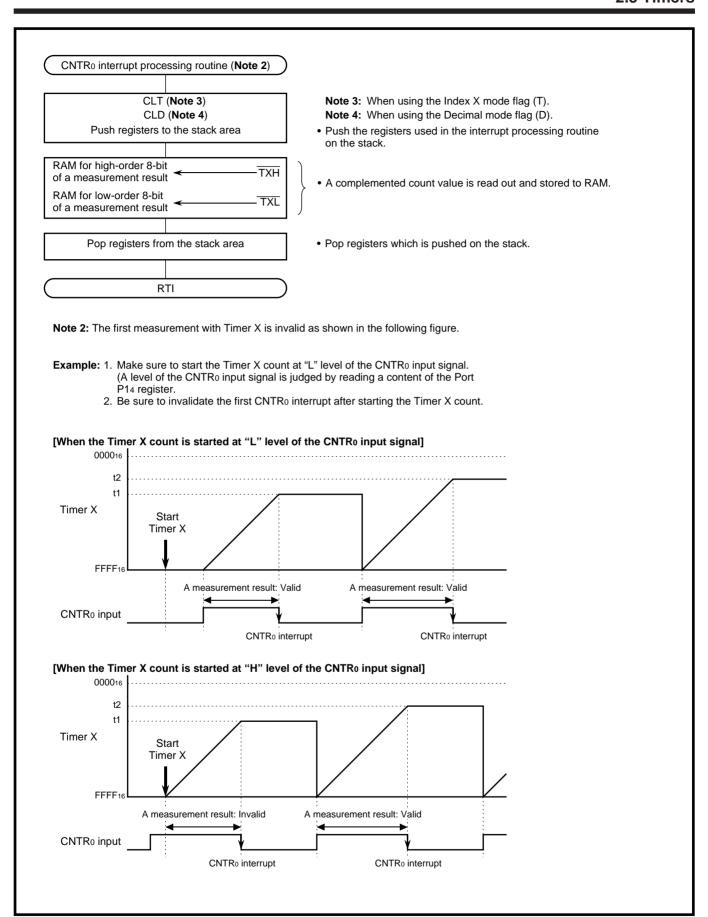

|                                         | surement of pulse width] (1)                                                                   |      |

|                                         | surement of pulse width] (2)                                                                   |      |

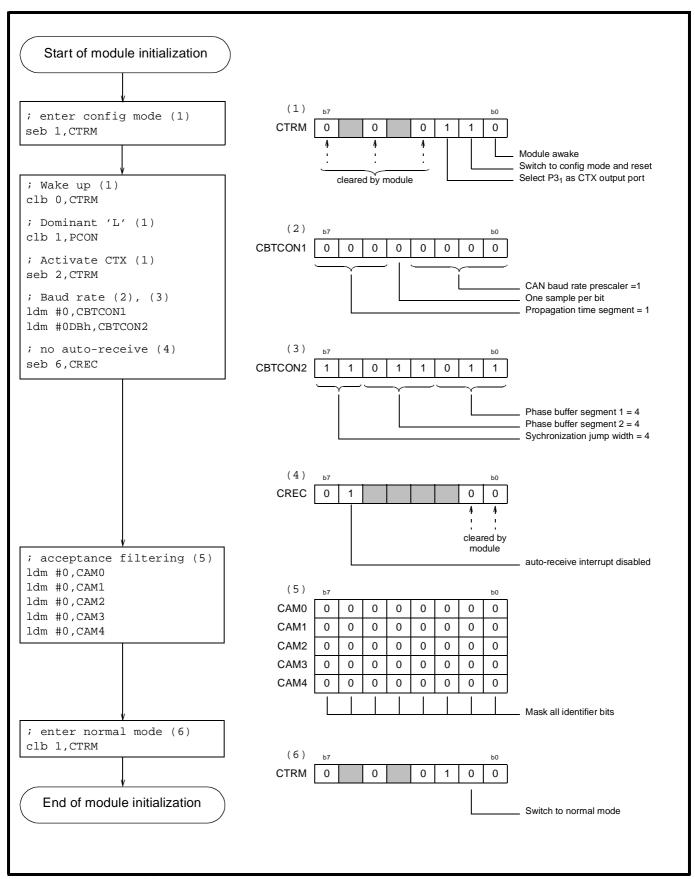

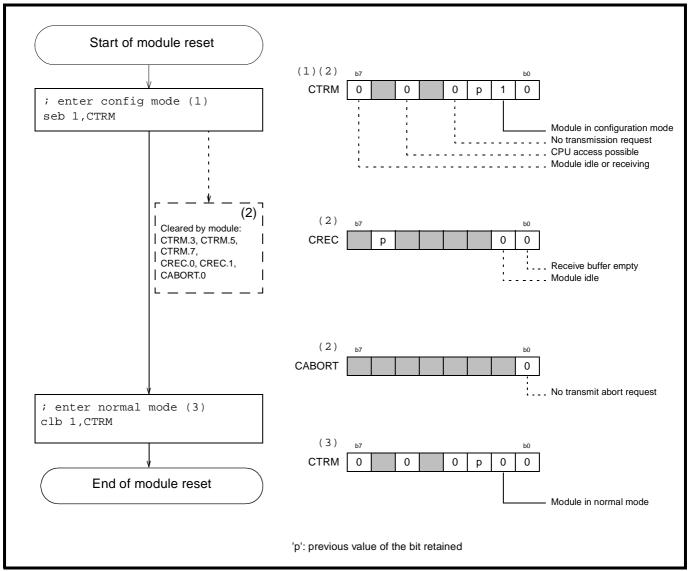

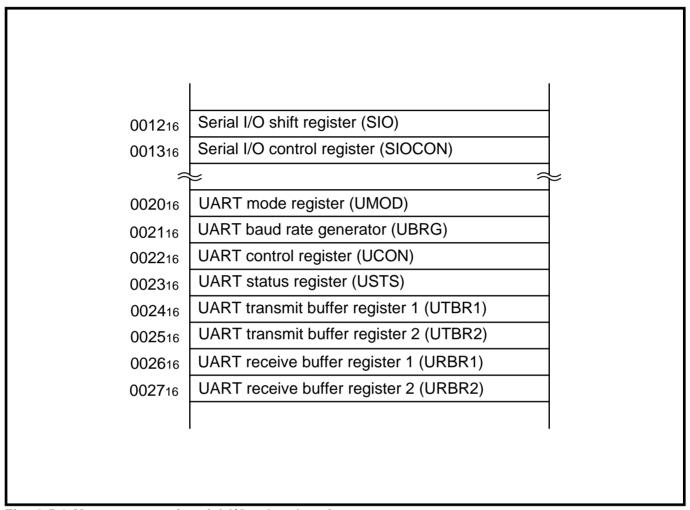

| -                                       | odule                                                                                          |      |

|                                         | ated registers                                                                                 |      |

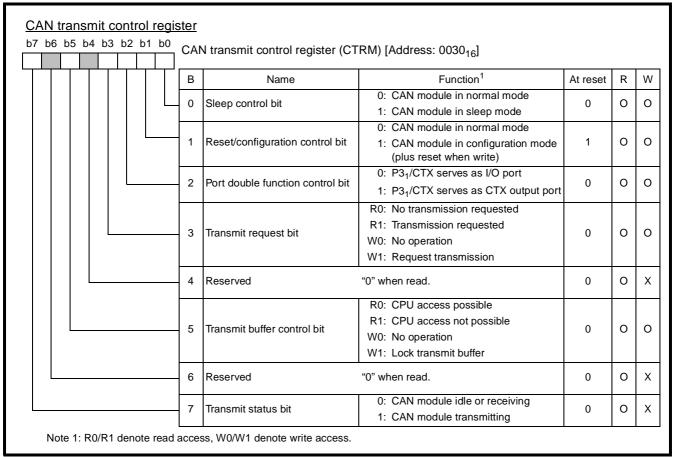

| =                                       | it control register                                                                            |      |

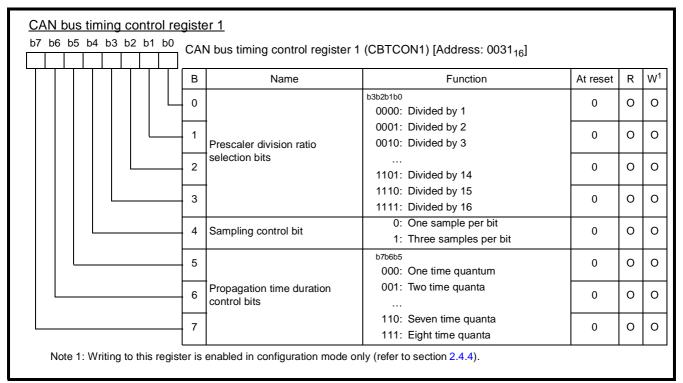

| _                                       | ning control register 1                                                                        |      |

| Fig. 2.4.5 Structure of CAN bus time    | ning control register 2                                                                        | 2-38 |

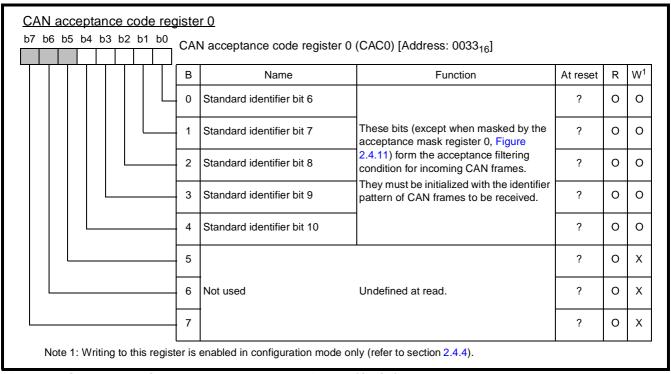

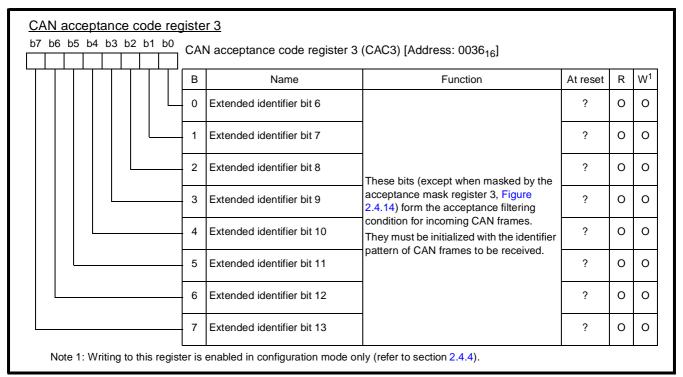

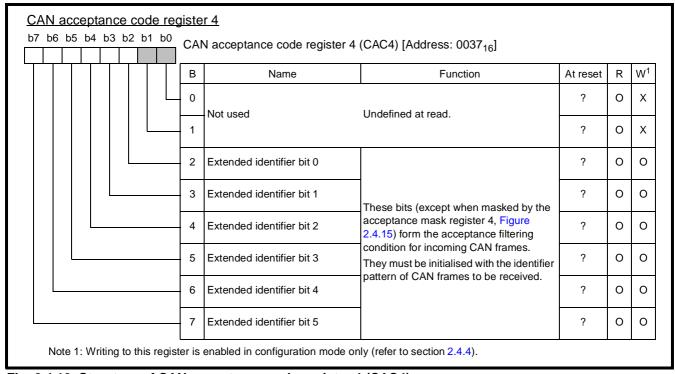

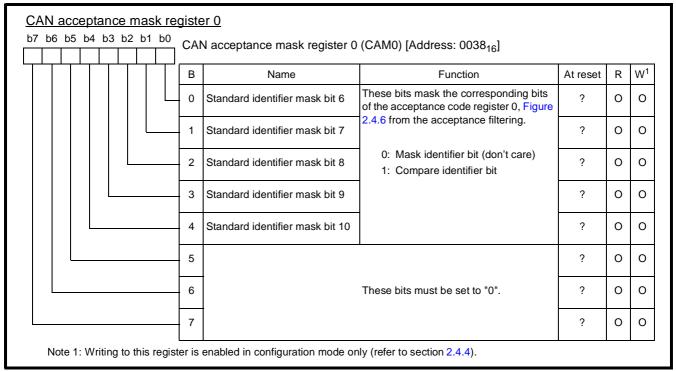

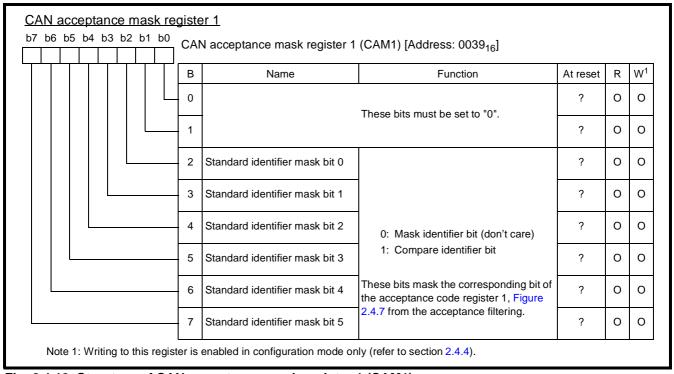

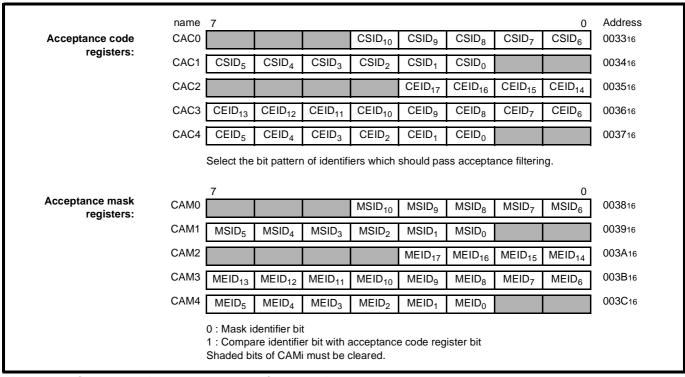

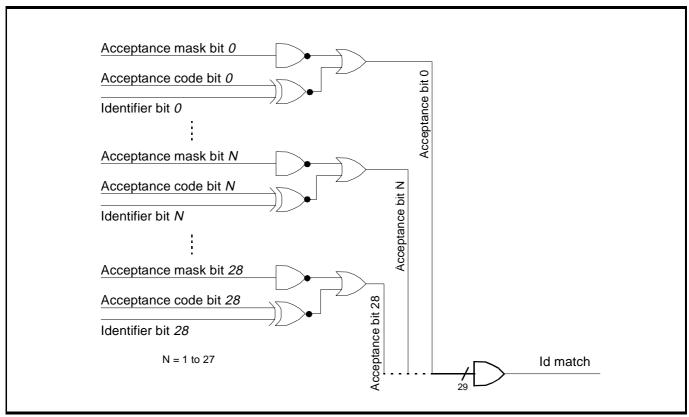

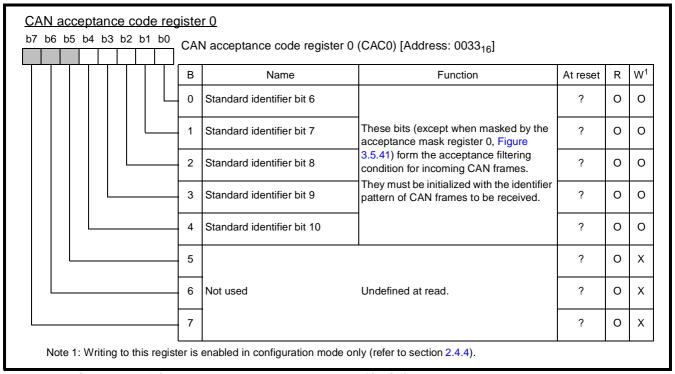

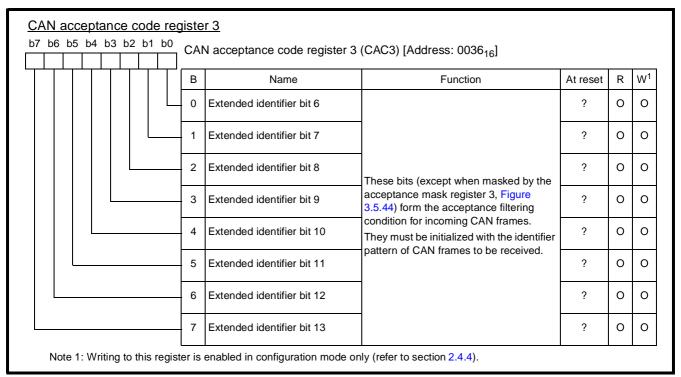

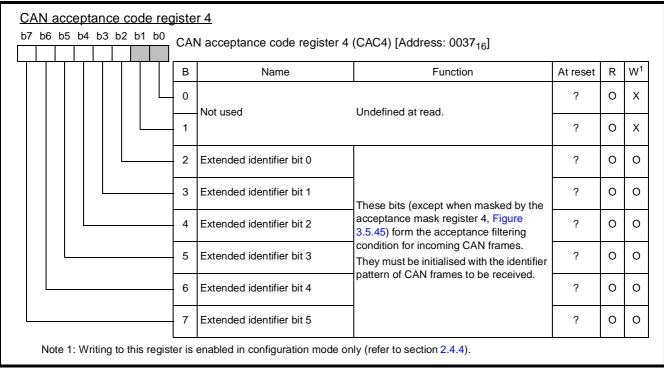

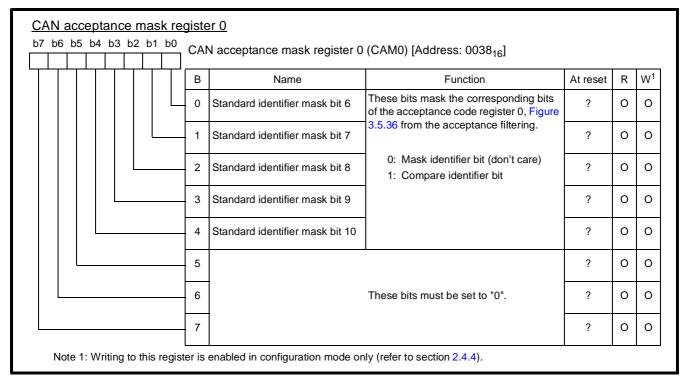

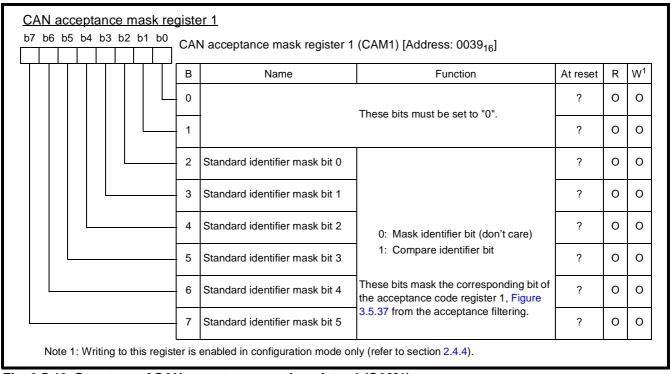

| 2.4.6 Structure of CAN acceptance code register 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 2-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

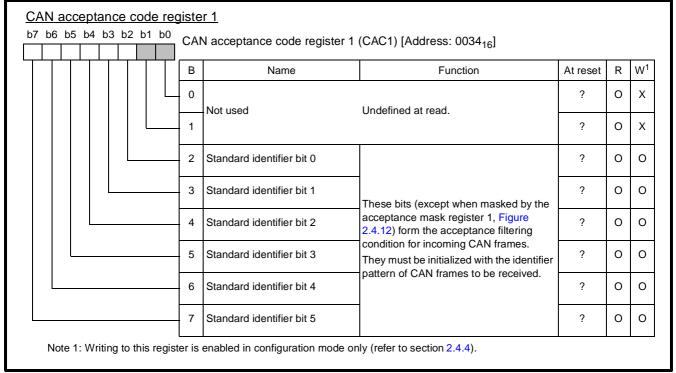

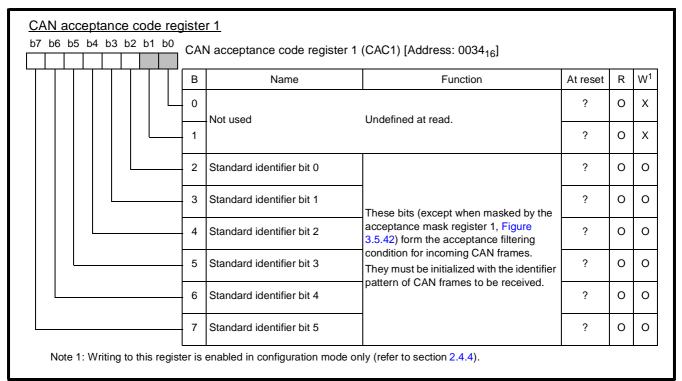

| 2.4.7 Structure of CAN acceptance code register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 2-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

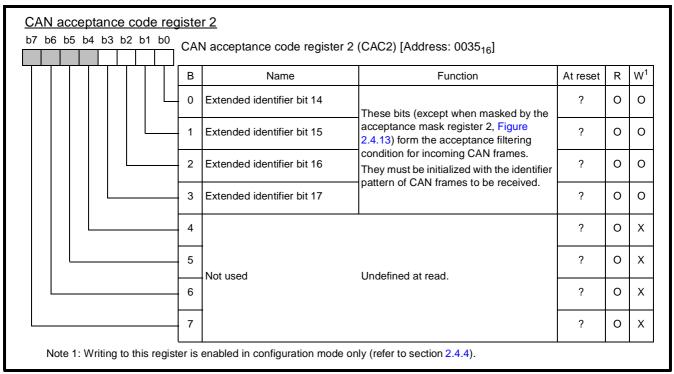

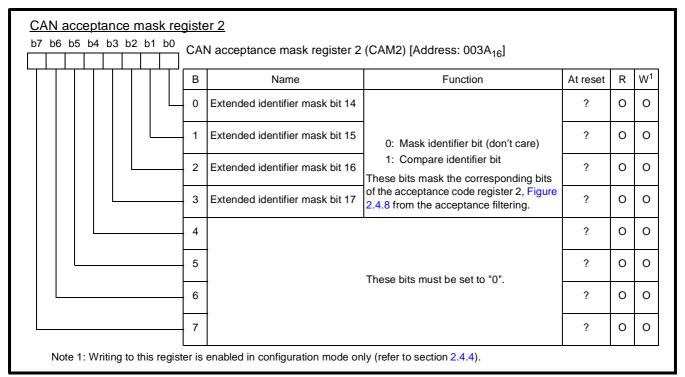

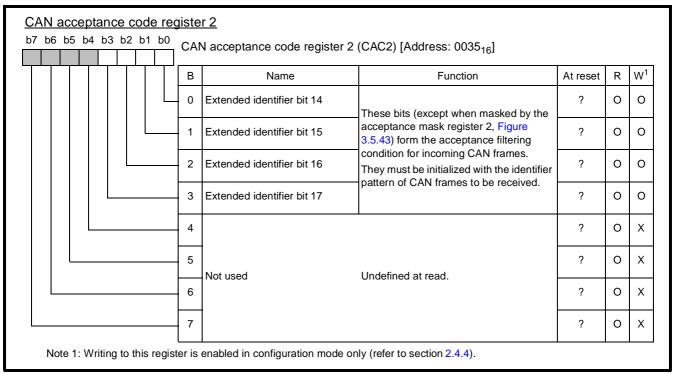

| 2.4.8 Structure of CAN acceptance code register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 2-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |